When it was brought up on our internal OCP team call recently that we should streamline our event terminology, I jumped at the opportunity. I’m nothing if not a fan of efficiency and consolidation. Our event team took some time over the last few days to review our Summit lingo and made some co (...)

Technology Demonstrations

Lisbon, Portugal

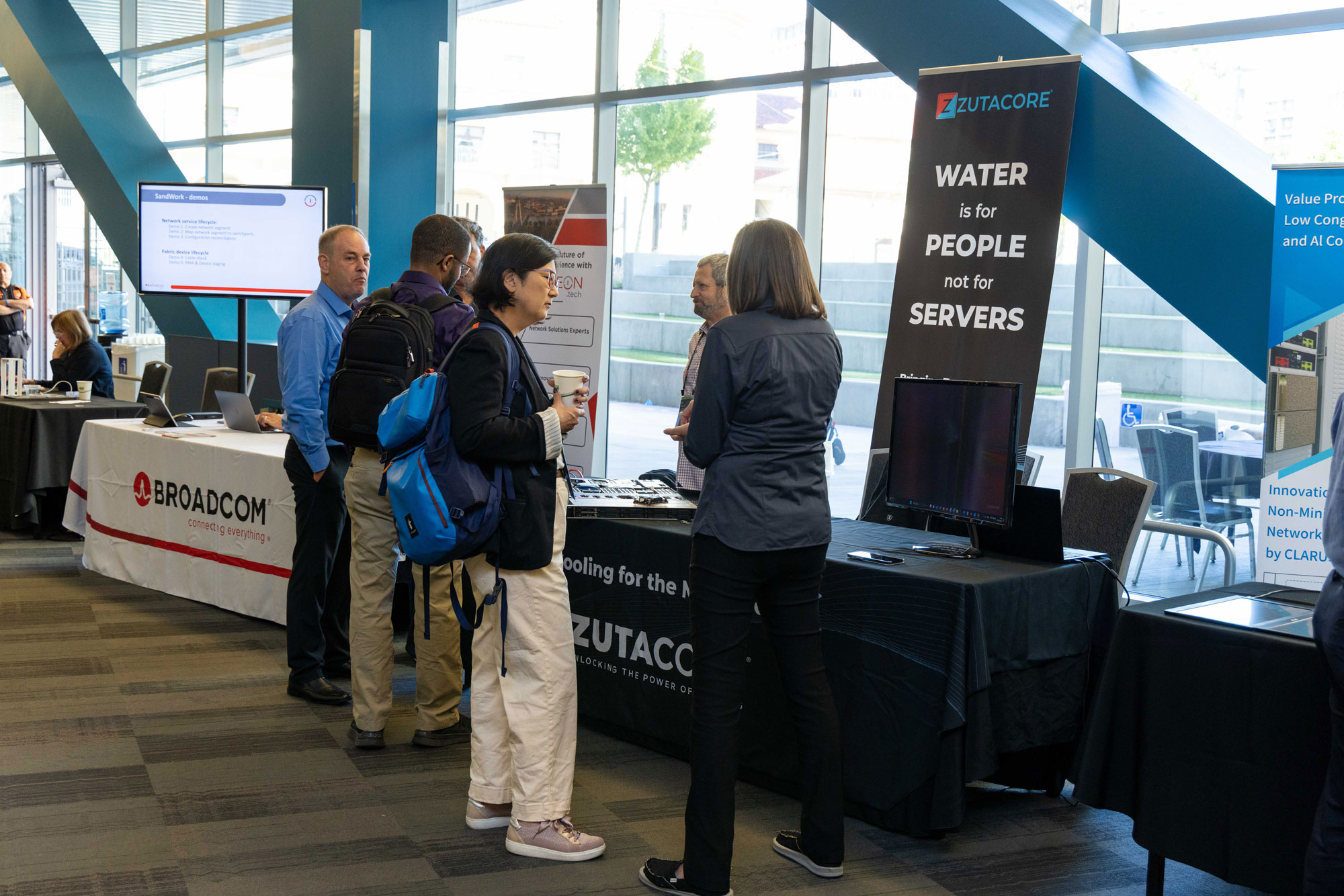

Technology Demonstrations

The OCP Future Technologies Symposium (FTS) Tech. Demonstration is an experiential session of the Symposium, where participants have an interactive, hands-on experience with future technologies. These demonstrations include innovative live models, physical prototypes, simulations, near-to-market solutions showcasing future technologies.

Come see the interactive experiences of cutting-edge technologies of the Tech. Demos at OCP FTS.

2024 Regional FTS Tech Demo Highlights

Blindspot Software

Blindspot Software

We like to showcase our Firmware Testing solution FirmwareCI. We are part of the OCP Startup Program and are excited to join the FTS Tech Demo this year! We worked very hard during the last month to enable this on OCP Server such as OCP Deltalake or Tiogapass - and we are currently working with the OCP S.A.F.E. program for possible collaboration.

Lightelligence

Lightelligence

Lightelligence will demonstrate the world’s first optical communications hardware to provide PCIe 5.0 and Compute Express Link (CXL) connectivity, producing significant benefits for AI computing applications. The exhibit will illustrate decode throughput improvements when running LLM inference using optically connected CXL memory, as compared to using traditional memory. Optically connected memory will reveal significant latency and energy efficiency compared to the current technology, allowing data center managers to scale CPU/GPU and memory resources across several racks. Optics has inherent advantages compared to copper which is typically used for PCIe/CXL connectivity. The signal loss in copper is quite high, even over short distances and can only scale a few meters. However optical PCIe/CXL can scale to 10s of meters and is only limited by the speed of light. The cross-sectional area of fiber optics is dramatically smaller than the bulky PCIe copper cables being used today.

London South Bank University

London South Bank University

The CEDaCI project was launched to kick start a Circular Economy for the Data Centre Industry. A key output is the Circular Data Centre Compass - a free to use digital tool that enables stakeholders to make informed decisions about three key life cycle stages: the benefits of Product Life Extension (reuse) , Recycling at end-of-life and Design for Circularity. The unique tool is based on empirical data and the most accurate and up-to-date Life Cycle Sustainability Assessment data

ZPT-ZeroPoint Technologies

ZPT-ZeroPoint Technologies

We are set to showcase a hardware-accelerated approach to in-line memory compression/decompression and compressed memory management. Our demonstration will illustrate a practical application of Memory Tiering within a CXL device, introducing Hardware compressed CXL memory as a novel tier in the Memory Hierarchy. As a pivotal guide to the CXL Community, Hyperscalers have formulated the groundbreaking OCP Hyperscale CXL Tiered Memory Expander Specification. If implemented, this specification lowers TCO adoption barriers, enabling diverse CXL deployments at both Hyperscaler and Enterprise levels. We present a CXL integrated solution, aligning with the aforementioned specification, introducing an energy-efficient, scalable, Hardware-accelerated, Lossless Compressed Memory CXL Tier. This solution is open for integration with Memory Expander controller manufacturers, offers 2-4X CXL memory compression in nanoseconds, delivering a 20-25% reduction in TCO for end customers without requiring additional physical slots. Our Tech Demos will provide participants with Early Access interactive, hands-on experience with an OCP Spec compliant, near future technology slated for mid-2024 production. From our demonstration, the audience can gain valuable insights into the practical implementation of a Composable Memory system using CXL, closely aligned to the Hyperscale CXL Tiered Memory Expander Specification. The audience will benefit from a live demonstration of real time Tier capacity adjustments to varying compression/decompression ratios on a wide range of Data Center workloads.

proteanTecs

proteanTecs

The ever-growing demands of AI and HPC are pushing the boundaries of chip architecture, making advanced chiplet solutions essential. However, ensuring reliability in these complex systems remains a challenge. This demo showcases a novel in-chip monitoring technique for advanced 2.5D/3D packaging, addressing a critical challenge in the AI/HPC industry: ensuring chiplet interconnect reliability. Traditional testing methods fall short due to the hidden nature of chiplet-to-chiplet interfaces. This hands-on demo presents in-chip monitoring and parametric lane grading, that enables comprehensive insights on performance degradation and high-precision outlier detection and lane swapping. This technology addresses a crucial need for the AI/HPC community, paving the way for wider chiplet adoption in mission-critical applications.

If you have any questions regarding the 2024 OCP Future Technologies Symposium, please contact Lesya Dymyd, FTS Chair