# OCP Universal Baseboard (UBB) Design Specification v1.5

**Author: OCP OAI Workstreams**

# **Contents**

| 1. | License                                              | 9                                     |          |

|----|------------------------------------------------------|---------------------------------------|----------|

| 2. | Acknowledgment                                       | 10                                    |          |

| 3. | Introduction and Scope                               | 11                                    |          |

| 4. | Universal Baseboard (OAI-UBB) High-level Description | 13                                    |          |

| 5. | Input and Output Interfaces                          | 15                                    |          |

|    | 5.1. OAM Interconnect Interface                      |                                       | 15       |

|    | 5.2. Host Fabric Interface                           |                                       | 16       |

|    | 5.2.1. Host Interface: High-speed interface          |                                       | 16       |

|    | 5.2.2. Pin list                                      |                                       | 16       |

|    | 5.3. Scale-Out Interface                             |                                       | 16       |

|    | 5.3.1. High-speed support                            |                                       | 17       |

|    | 5.3.2. I2C                                           |                                       | 17       |

|    | 5.3.3. Pin list                                      |                                       | 17       |

|    | 5.4. Miscellaneous Signal Interface                  |                                       | 17       |

|    | 5.4.1. Clock and I2C Signals                         |                                       | 17       |

|    | 5.4.2. Board management                              | ;                                     | 17       |

|    | 5.4.3. Power management                              |                                       | 17       |

|    | 5.5. Input Power Interface                           |                                       | 18       |

|    | 5.5.1. UBB System Power                              | :                                     | 18       |

|    | 5.5.2. 54V/48V based OAM power input                 |                                       | 19       |

|    | 5.5.3. 12V based OAM Power input                     |                                       | 20       |

|    | 5.5.4. OAM Excursion Power Support                   | :                                     | 20       |

|    | 5.6. 40V ~ 59.5V power layout guidance               | :                                     | 21       |

| 6. | UBB Electrical Specification                         | 23                                    |          |

|    | 6.1. Board Architecture specification                |                                       | 23       |

|    | 6.1.1. System Clock Architecture                     |                                       | 23       |

|    | 6.1.2. I2C architecture                              |                                       | 23       |

|    | 6.1.3. Power control                                 |                                       | 24       |

|    | 6.1.4. Reset                                         |                                       | 25       |

|    | 6.1.5. Power Diagram                                 |                                       | 26       |

|    | 6.1.6. Strap pins                                    |                                       | 26       |

|    | 6.1.6.1. Module ID                                   |                                       | 26       |

|    | 6.1.6.2. Link_Config[4:0]<br>6.1.6.3. PE BIF[1:0]    |                                       | 28       |

|    | 6.1.6.3. PE_BIF[1:0] 6.1.7. Debug interface          |                                       | 28<br>28 |

|    | 6.1.8. JTAG Interface                                |                                       | 28<br>28 |

|    | 6.1.9. UART                                          |                                       | 20<br>30 |

|    | 6.1.10. Debug Header                                 |                                       | 30       |

|    | 6.1.11. UBB Power sequence                           |                                       | 31       |

|    | 6.1.12. FRU                                          |                                       | 33       |

|    | 6.2. UBB Connectors                                  |                                       | 35       |

|    | o.z. odd connectors                                  | · · · · · · · · · · · · · · · · · · · | رر       |

|    | 6.2.1 | UBB Connector pin list                               |          | 35         |

|----|-------|------------------------------------------------------|----------|------------|

|    | 6.    | 5.2.1.1. QSFP-DD connector pin list                  |          | 35         |

|    | 6.    | 5.2.1.2. 54V power connector pin list                |          | 37         |

|    |       | 5.2.1.3. 12V power connector pin list                |          | 39         |

|    |       | 5.2.1.4. 12V power connector re-purpose for 54V      |          | 40         |

|    |       | 5.2.1.5. Host Interface Connector (HIF) pin list     |          | 40         |

|    | 6.    | 5.2.1.6. OAM Debug connector pin list                |          | 49         |

|    | 6.3.  | PCB Stack-Up                                         |          | 51         |

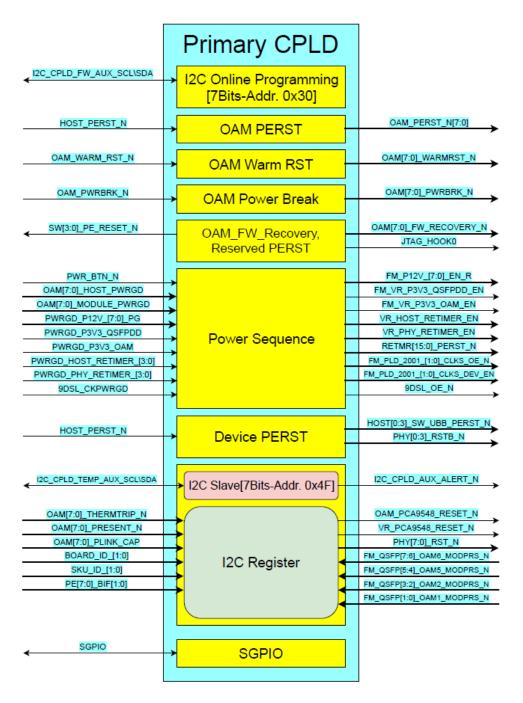

|    | 6.4.  | CPLD                                                 |          | 53         |

|    | 6.4.1 | 1. Block Diagram of UBB Primary CPLD                 |          | 53         |

|    | 6.4.2 | ,                                                    |          | 55         |

|    | 6.4.3 | 3                                                    |          | 55         |

|    | 6.4.4 |                                                      |          | 55         |

|    | 6.4.5 | 5. Reserved PERST for Multi-host                     |          | 58         |

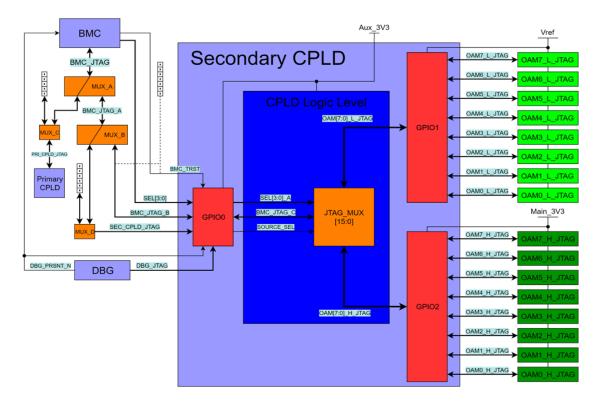

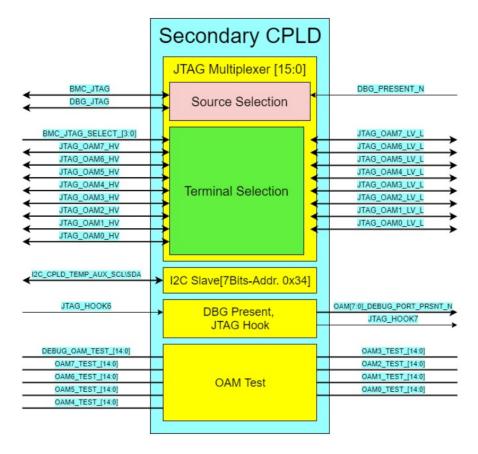

|    | 6.5.  | Block Diagram of UBB Secondary CPLD                  |          | 58         |

|    | 6.5.1 | <ol> <li>JTAG and debug present</li> </ol>           |          | 59         |

|    | 6.5.2 |                                                      |          | 60         |

|    | 6.5.3 | ·                                                    |          | 60         |

|    | 6.5.4 | •                                                    |          | 61         |

|    | 6.5.5 |                                                      |          | 61         |

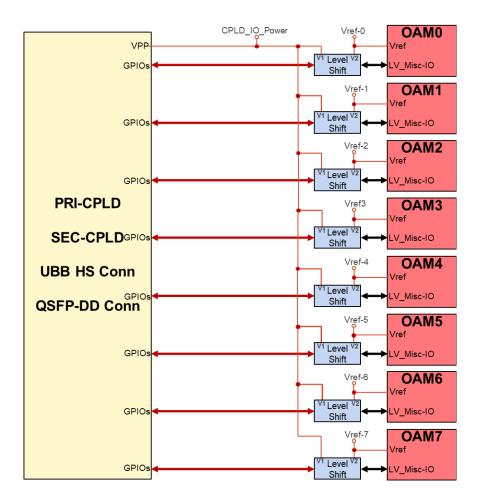

|    | 6.5.6 | 6. OAM Vref based IO Pin                             |          | 69         |

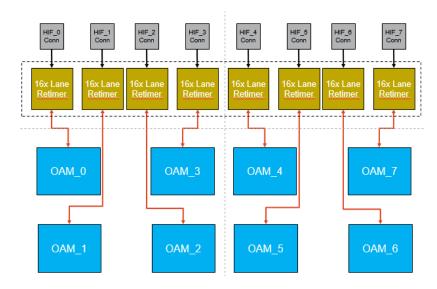

|    | 6.6.  | Host retimer                                         |          | 71         |

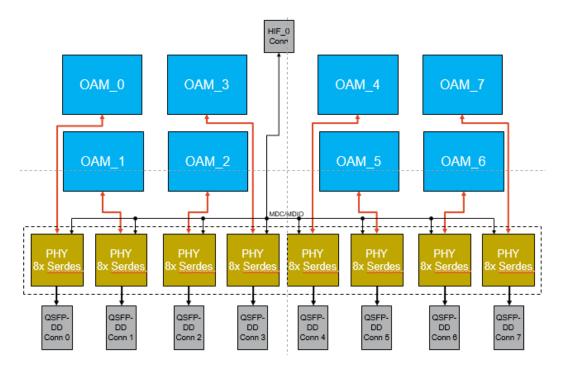

|    | 6.7.  | SERDES PHY Retimer                                   |          | 71         |

|    | 6.8.  | High-Speed SI guidance                               |          | 72         |

| 7. | Inte  | erconnect Topology                                   |          | 73         |

|    | 7.1.  | Module ID                                            |          | 73         |

|    | 7.2.  | LINK_CONFIG ID                                       |          | <b>7</b> 3 |

|    | 7.3.  | Combined Fully Connected and 6-port Hybrid Cube Mesh | Topology | 74         |

|    | 7.4.  | 8-port Hybrid Cube Mesh Topology                     |          | 76         |

|    | 7.5.  | UBB Reference boards                                 |          | 77         |

|    | 7.6.  | UBB silkscreen                                       |          | 77         |

| 8. | Med   | chanical Specification                               |          | 79         |

|    | 8.1.  | Board dimension                                      |          | 79         |

|    | 8.2.  | Required Components                                  |          | 80         |

|    | 8.2.1 | ·                                                    |          | 80         |

|    | 8.2.2 | 2. I/O Connectors                                    |          | 82         |

|    | 8.2.3 | 3. Screw Mounting Holes                              |          | 84         |

|    | 8.3.  | Recommended Components                               |          | 87         |

|    | 8.3.1 |                                                      |          | 87         |

|    | 8.3.2 |                                                      |          | 88         |

|    | 2 /   | Assembly                                             |          | ٩٢         |

|    |       |                                                      |          |            |

|     | 8.4.1.              | Screw Torque                        |     | 90  |

|-----|---------------------|-------------------------------------|-----|-----|

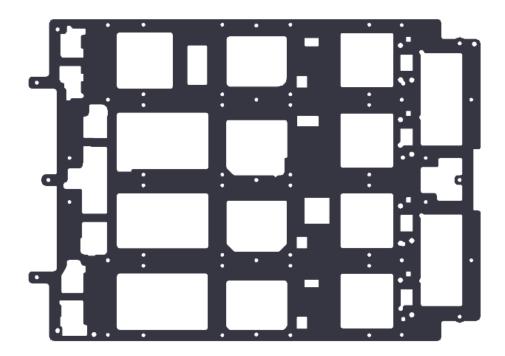

|     | 8.4.2.              | Reference Bolster Plate             |     | 90  |

|     | 8.4.3.              | Mylar                               |     | 91  |

| 9.  | Thern               | nal and Cooling Specification       | 93  |     |

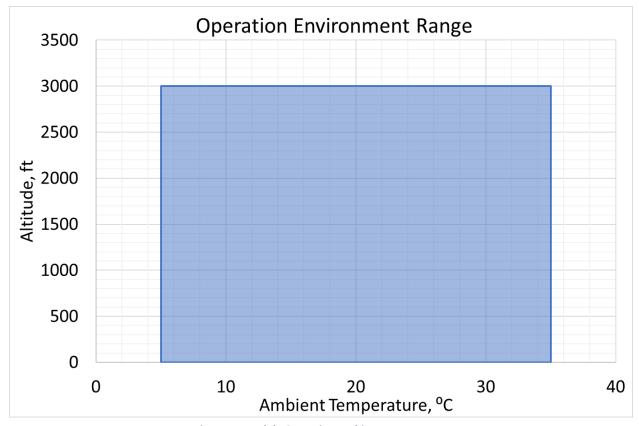

| 9.1 | L. E                | nvironmental Conditions             |     | 93  |

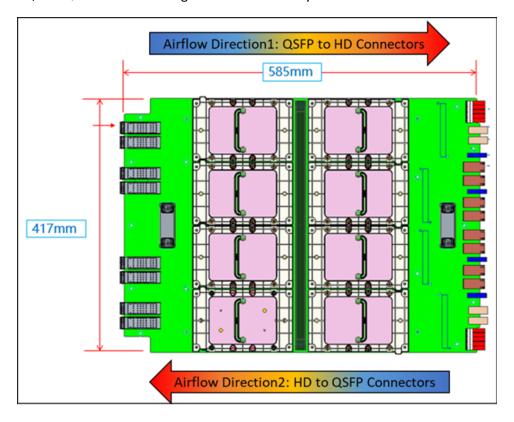

| 9.2 | <u>2</u> . <i>A</i> | Air Flow Direction                  |     | 93  |

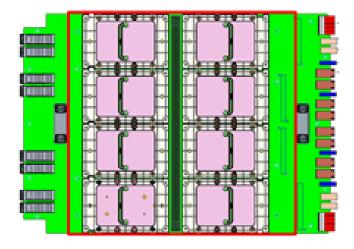

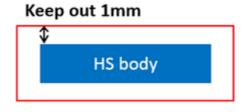

| 9.3 | 3. k                | Keep Out Zone                       |     | 94  |

| 9.4 | l. 1                | emperature Report                   |     | 95  |

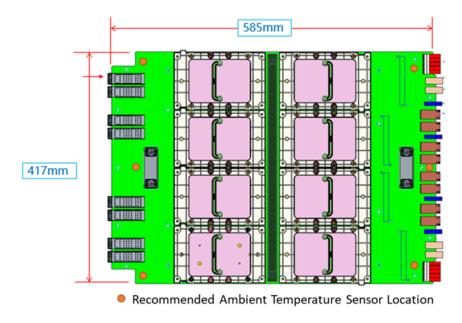

|     | 9.4.1.              | Temperature Sensors                 |     | 95  |

| 9.5 | 5. 1                | Thermal Recommendation              |     | 96  |

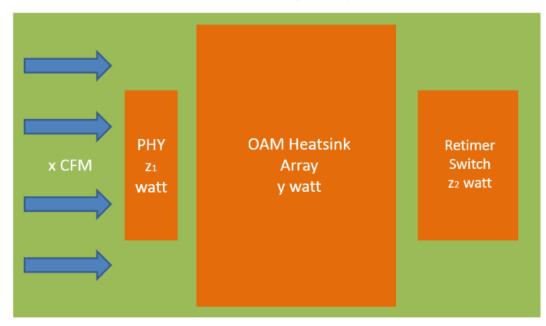

|     | 9.5.1.              | Airflow Budget                      |     | 96  |

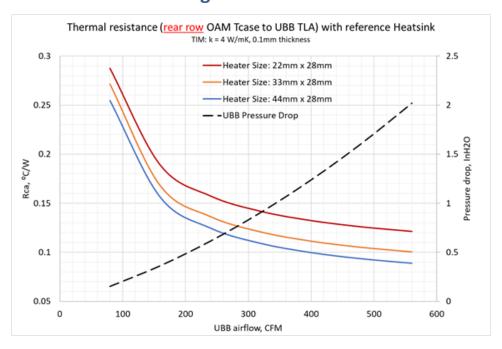

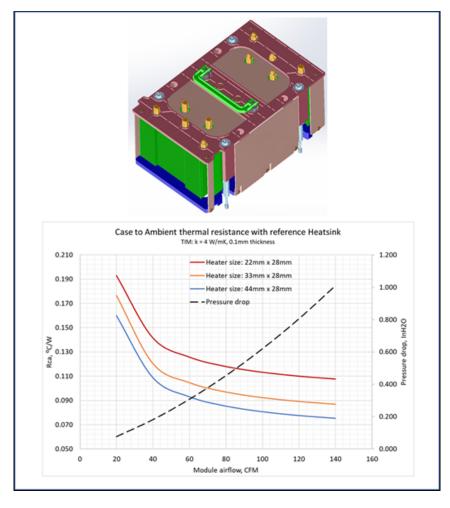

|     | 9.5.2.              | Reference Heatsink Design           |     | 97  |

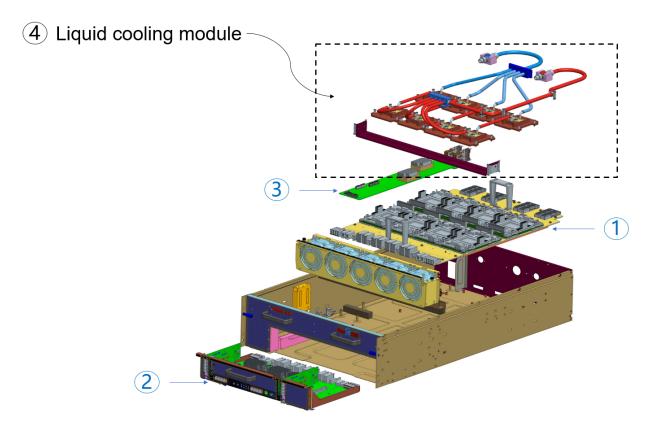

|     | 9.5.3.              | Reference Liquid Cooling Design     |     | 98  |

| 10. | Syste               | m Management                        | 101 |     |

| 10  | .1. l               | JBB I2C Topology                    |     | 101 |

| 10  | .2. 9               | Sensors and Events                  |     | 101 |

| 10  | .3. ι               | JBB FRU Format                      |     | 105 |

| 11. | 54V/4               | 8V Safety Requirement               | 111 |     |

| 11  | .1. F               | Pollution Degrees                   |     | 111 |

| 11  | .2. [               | Determination of minimum clearances |     | 112 |

| 11  | .3. (               | Creepage and Clearance in Practice  |     | 112 |

| 12. | Acron               | yms                                 | 113 |     |

| 13. | Revisi              | on History                          | 114 |     |

# **Figures**

| Figure 1 OAI as a disaggregated compute for AI in a Rack.                                  | 11 |

|--------------------------------------------------------------------------------------------|----|

| Figure 2 OAI building blocks                                                               | 12 |

| Figure 3 Example OAI System Building Blocks                                                | 13 |

| Figure 4 Example UBB System Building Blocks                                                | 14 |

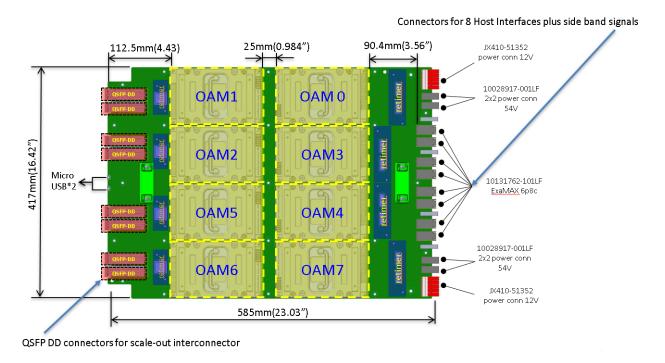

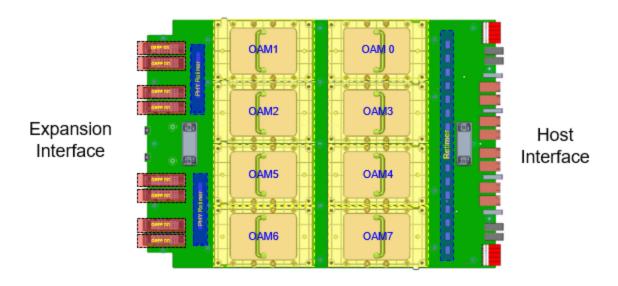

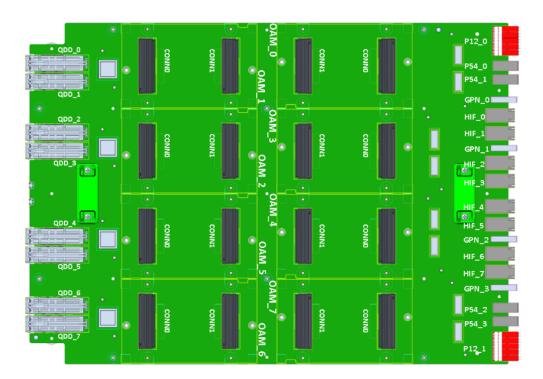

| Figure 5 Universal Reference Base Board (UBB)                                              | 15 |

| Figure 6 UBB Host and Expansion (scale-out) Interfaces                                     | 16 |

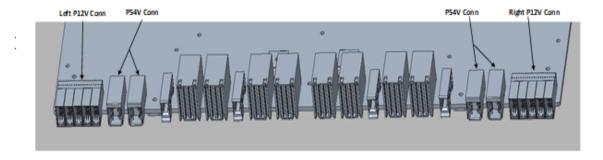

| Figure 7 Input Power connectors Placement                                                  | 18 |

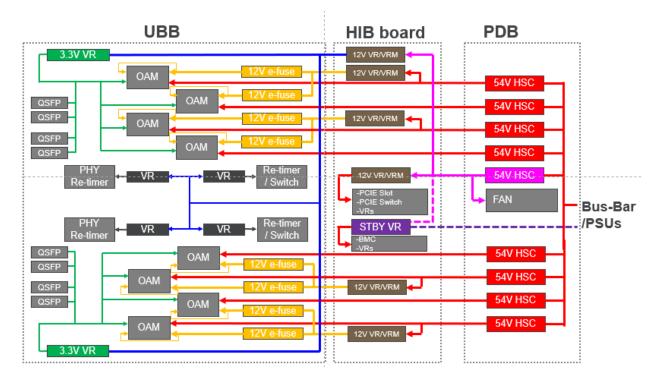

| Figure 8 OAI Reference UBB power Delivery Diagram                                          | 18 |

| Figure Figure 9 Cmin calculation for OAM peak current                                      | 21 |

| Figure 10 power and GND isolation                                                          | 22 |

| Figure 11 OAI Reference UBB clock diagram                                                  | 23 |

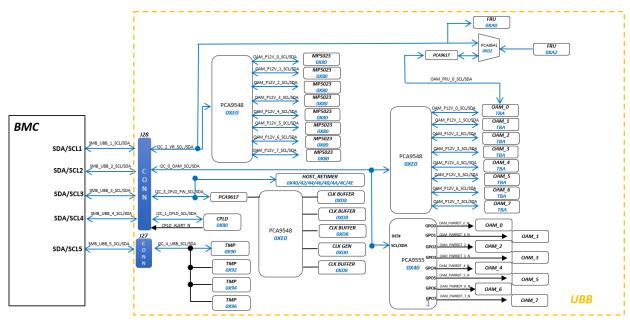

| Figure 12 I2C/SMBus Block Diagram                                                          | 24 |

| Figure 13 UBB Reset signals diagram                                                        | 25 |

| Figure 14 Power Control Block Diagram                                                      | 26 |

| Figure 15 Required MODULE_ID[4:0] assignments for baseboards with 8 interconnected modules | 27 |

| Figure 16 Module_ID[4:0] assignments when four only in two rows of two                     | 27 |

| Figure 17 JTAG diagram                                                                     | 29 |

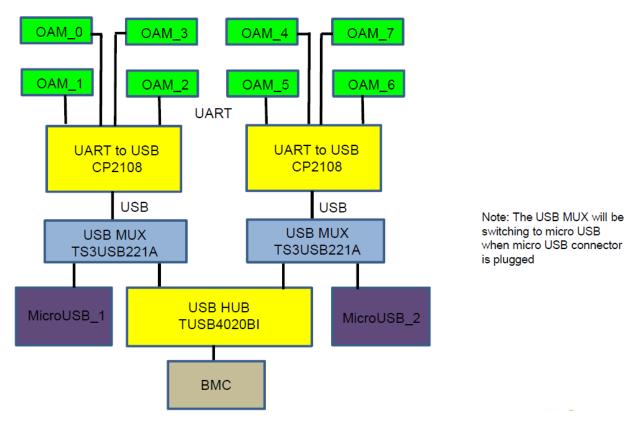

| Figure 18 UART Diagram                                                                     | 30 |

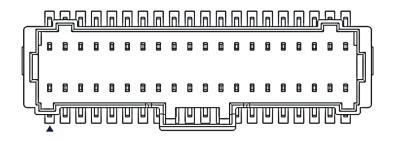

| Figure 19 UBB reference board debug header                                                 | 31 |

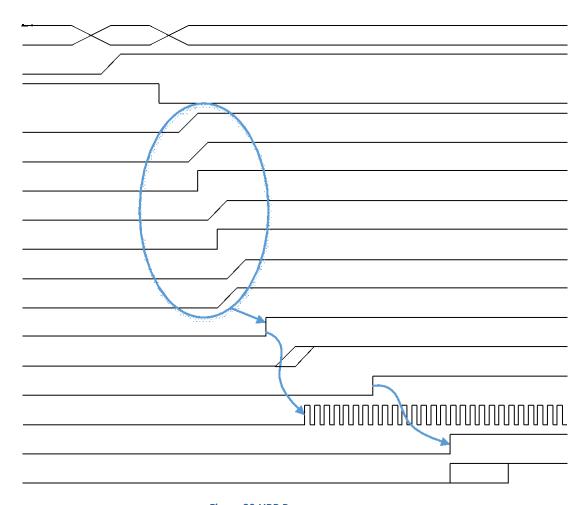

| Figure 20 UBB Power-on sequence                                                            | 32 |

| Figure 21 UBB Power-down sequence                                                          | 33 |

| Figure 22 DC is off, BMC switches FRU1 access to BMC                                       | 34 |

| Figure 23 When DC is on, BMC switches FRU1 access to OAM0                                  | 34 |

| Figure 24 54V power connector                                                              | 38 |

| Figure 25 12V power connector pin list                                                     | 39 |

| Figure 26 Primary CPLD diagram                                                             | 54 |

| Figure 27 Secondary CPLD Diagram                                                           | 59 |

| Figure 28 Vref Signal Block Diagram                                                        | 70 |

| Figure 29 HIB Lane Retimer Topology                                                        | 71 |

| Figure 30 UBB Scale-Out Serdes PHY Topology (Example)                                      | 72 |

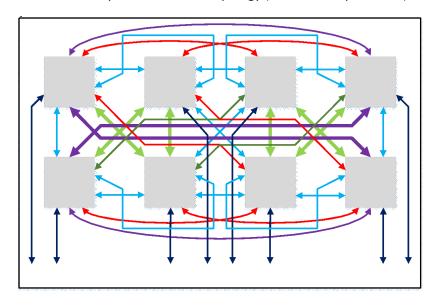

| Figure 31 LINK_CONFIG ID                                                                   | 74 |

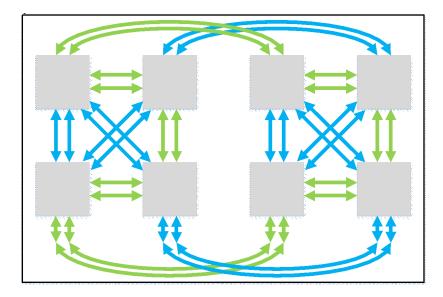

| Figure 32 Combined FC/6-Port HCM Topology                                                  | 75 |

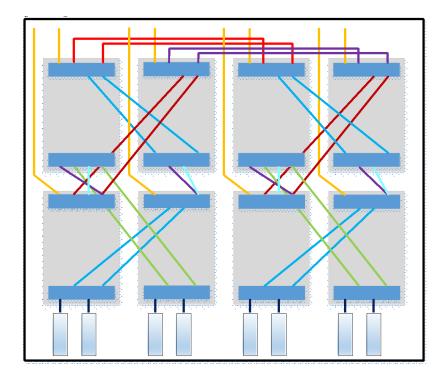

| Figure 33 Detail port mapping and routing guidance                                         | 75 |

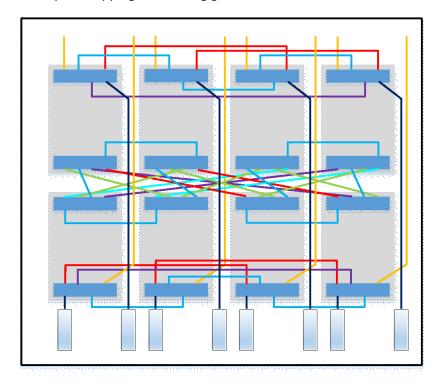

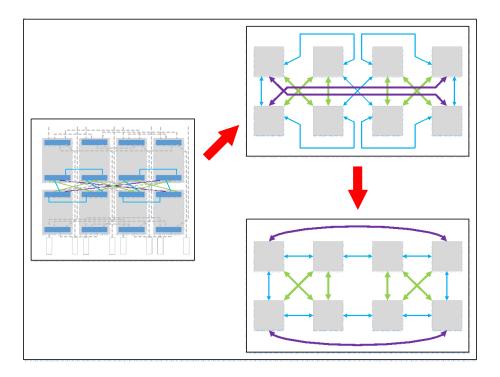

| Figure 34 Embedded HCM Topology                                                            | 76 |

| Figure 35 8-port Hybrid Cube Mesh Topology                                                 | 76 |

| Figure 36 8-port HCM topology routing guide                                                | 77 |

| Figure 37 UBB silkscreen example                                                           | 78 |

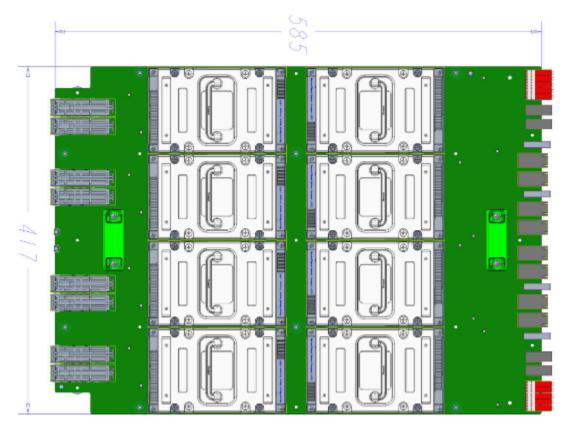

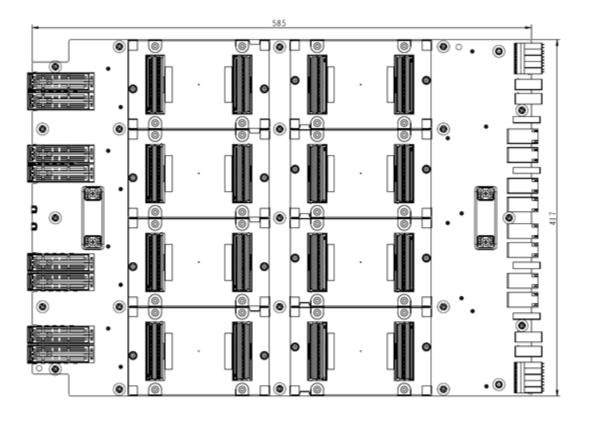

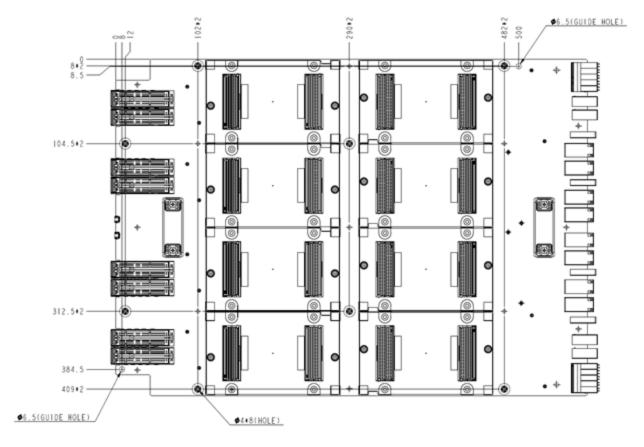

| Figure 38 UBB board dimension                                                              | 79 |

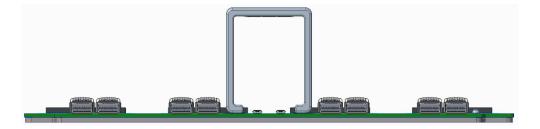

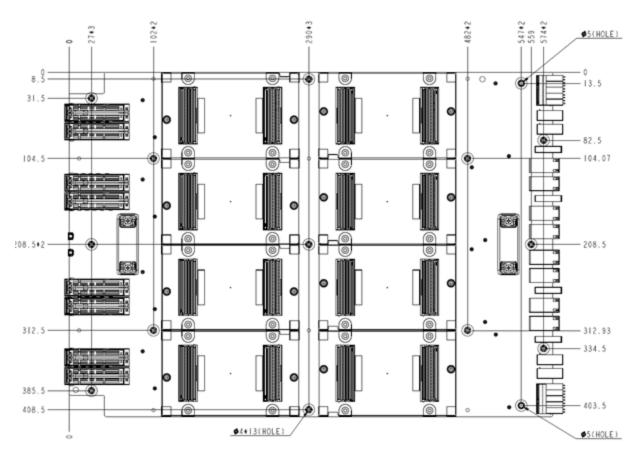

| Figure 39 UBB board Top and side views                                                     | 80 |

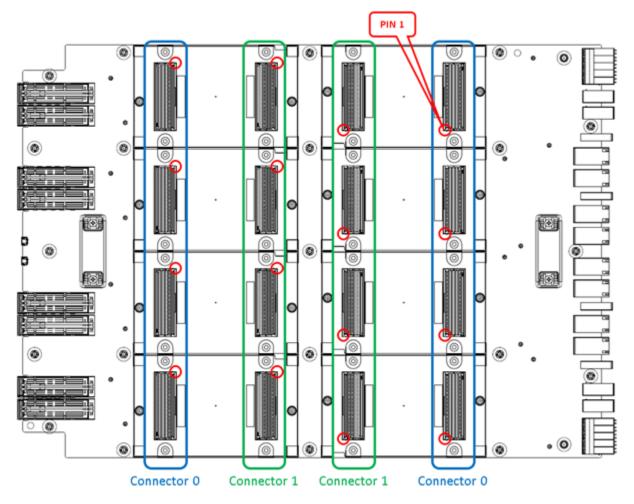

| Figure 40 OAM Mirror Mezz Pro connector pin1 orientation_FC                                | 81 |

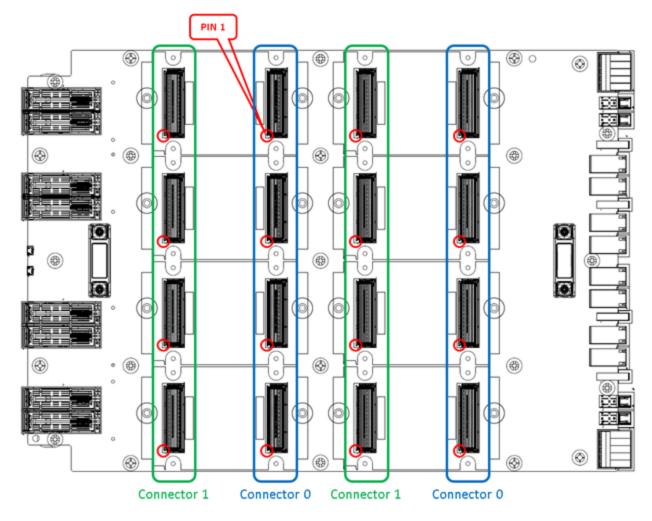

| Figure 41 OAM Mirror Mezz Pro connector pin1 orientation_HCM                               | 82 |

| Figure 42 UBB Front IOs                                                                    | 83 |

| Figure 43 UBB high speed and power connectors to HIB                                       | 83 |

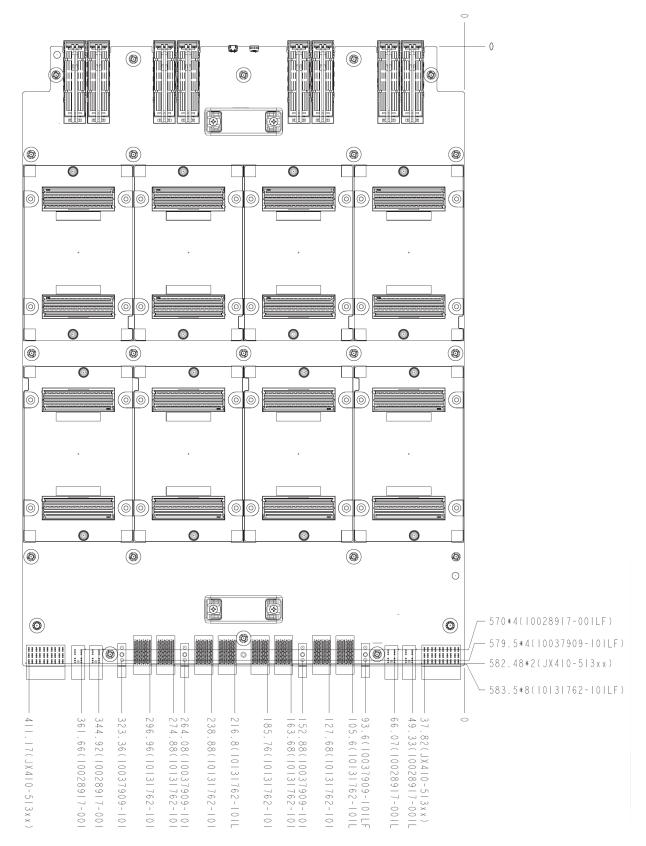

| Figure 44 UBB high speed and power connectors coordinate                                   | 84 |

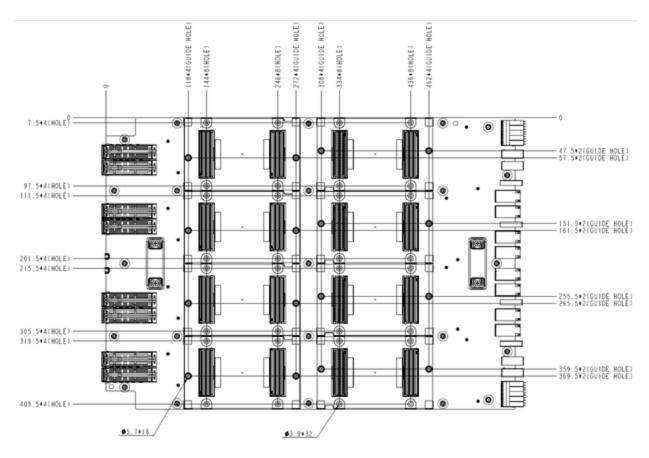

| Figure 45 mounting holes                                                                   | 85 |

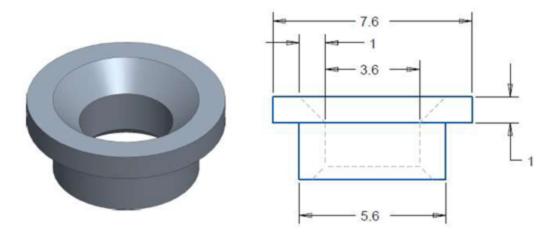

| Figure 46 OAM through holes                                                                | 86 |

| Figure 47 OAM guide hole                                                                   | 86 |

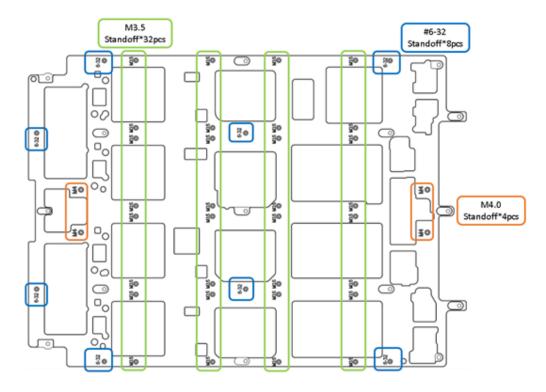

| Figure 48 Mounting holes for bolster                                                                             | 87  |

|------------------------------------------------------------------------------------------------------------------|-----|

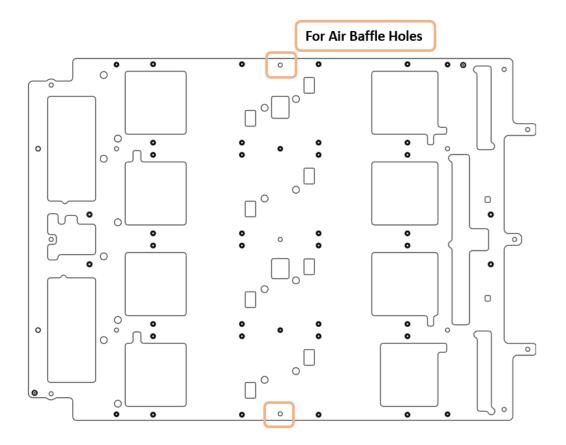

| Figure 49 Air Baffle mounting holes on the stiffener                                                             | 88  |

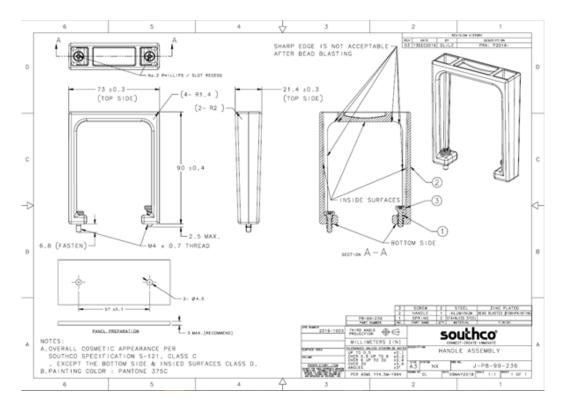

| Figure 50 Reference UBB handle                                                                                   | 89  |

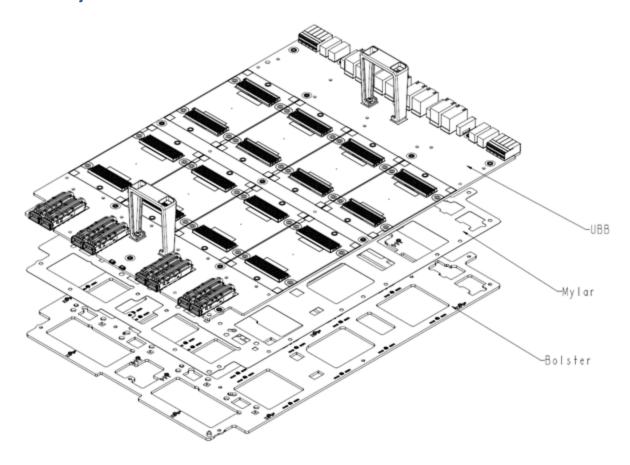

| Figure 51 UBB assembly DWG                                                                                       | 90  |

| Figure 52 Bolster plate reference design                                                                         | 91  |

| Figure 53 UBB mylar                                                                                              | 91  |

| Figure 54 Module Operation Ambient Temperature                                                                   | 93  |

| Figure 55 UBB at different airflow directions                                                                    | 94  |

| Figure 56 UBB heatsink recommended airflow area keep out                                                         | 94  |

| Figure 57 small heatsink keep out                                                                                | 95  |

| Figure 58 Recommended Ambient Temperature Sensor Map                                                             | 95  |

| Figure 59 CFM per Watt definition for UBB                                                                        | 96  |

| Figure 60 Thermal resistance and air pressure drop of UBB based on reference OAM Heatsink                        | 97  |

| Figure 61 Thermal resistance of single OAM Reference Heatsink                                                    | 98  |

| Figure 62 Reference Liquid Cooling Design for UBB. 1: Universal Base Board; 2: Host Interface Board; 3: Power    |     |

| Distribution Board; 4: Liquid Cooling Module. The cooling components and OAMs in the figure are just for concept |     |

| demonstration and do not represent real solutions.                                                               | 99  |

| Figure 63 UBB I2C Topology                                                                                       | 101 |

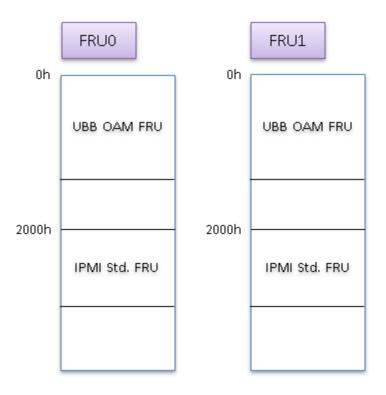

| Figure 64 FRU diagram                                                                                            | 105 |

| Figure 65 FRU0 and FRU1                                                                                          | 106 |

# **Tables**

| Table 1 Universal Based Board (UBB) is a building block                                               | 14 |

|-------------------------------------------------------------------------------------------------------|----|

| Table 2 UBB input voltage range                                                                       | 19 |

| Table 3 UBB(up to 700W OAM) input continuous current specifications                                   | 19 |

| Table 4 UBB(up to 700W OAM) EDP support example                                                       | 19 |

| Table 5 UBB operation voltage range                                                                   | 20 |

| Table 6 UBB input continuous current specifications                                                   | 20 |

| Table 7 UBB(up to 350w 12v based OAM) EDP support example                                             | 20 |

| Table 8 Cmin requirement at 2x EDP 20us                                                               | 21 |

| Table 9 40V ~ 59.5V layout guidance                                                                   | 22 |

| Table 10 MODULE_ID                                                                                    | 28 |

| Table 11 JTAG Truth Table                                                                             | 30 |

| Table 12 UBB debug header pin definition                                                              | 31 |

| Table 13 UBB connector list                                                                           | 35 |

| Table 14 QSFP-DD low-speed electrical specifications                                                  | 36 |

| Table 15 QSFP-DD connector 0~7 pin list                                                               | 37 |

| Table 16 P54V_0 Pin Definition                                                                        | 38 |

| Table 17 P54V_1 Pin Definition                                                                        | 38 |

| Table 18 P54V_2 Pin Definition                                                                        | 38 |

| Table 19 P54V_3 Pin Definition                                                                        | 39 |

| Table 20 P12V_0 power connector pin list                                                              | 39 |

| Table 21 P12V_1 power connector pin list                                                              | 39 |

| Table 22 HIF_0 connector pin list                                                                     | 41 |

| Table 23 HIF_1 connector pin list                                                                     | 42 |

| Table 24 HIF_2 connector pin list                                                                     | 44 |

| Table 25 HIF_3 connector pin list                                                                     | 45 |

| Table 26 HIF_4 connector pin list                                                                     | 47 |

| Table 27 HIF_5 connector pin list                                                                     | 48 |

| Table 28 HIF_6 connector pin list                                                                     | 48 |

| Table 29 HIF_7 connector pin list                                                                     | 49 |

| Table 30 OAM Debug connector pin list                                                                 | 50 |

| Table 31 UBB reference Stack-Up                                                                       | 52 |

| Table 32 UBB Impedance control                                                                        | 53 |

| Table 33 Primary COLD I2C Programming Slave                                                           | 55 |

| Table 34 Primary CPLD Fan-out to OAMs                                                                 | 55 |

| Table 35 Primary CPLD Slave I2C address for HIB                                                       | 55 |

| Table 36 Primary CPLD I2C slave register map                                                          | 58 |

| Table 37 JTAG debug present                                                                           | 60 |

| Table 38 OAM test pins definition                                                                     | 60 |

| Table 39 Secondary CPLD I2C Slave spec                                                                | 61 |

| Table 40 JTAG multiplexer of OAM                                                                      | 61 |

| Table 41 JTAG multiplexer terminal Selection                                                          | 61 |

| Table 42 Primary CPLD pin list                                                                        | 66 |

| Table 43 Secondary CPLD pin list                                                                      | 69 |

| Table 44 OAM Vref Signal usage                                                                        | 70 |

| Table 45 Mixed Voltage Support for LVCMOS and LVTTL I/O Types (copied from Lattice MachXO2 datasheet) | 71 |

| Table 46 UBB OAM module IDs                                                                           | 73 |

| Table 47 LINK_CONFIG[4:0] Encoding Definitions                                                        | 74 |

## Open Accelerator Infrastructure – Universal Baseboard Design Specification v1.5

| Table 48 UBB IO connectors              | 82  |

|-----------------------------------------|-----|

| Table 49 High speed and Power Conenctor | 83  |

| Table 50 Screw size and torque spec     | 90  |

| Table 51 SEL Definition List            | 102 |

| Table 52 Sensor name and Event table    | 104 |

| Table 53 FRU content-standard IPMI      | 106 |

| Table 54 UBB OAM Interconnect FRU       | 110 |

| Table 55 Minimum creepage distances     | 111 |

| Table 56 Altitude correction factors    | 112 |

| Table 57 Acronyms                       | 113 |

| Table 58 Revision History               | 116 |

# 1. License

Contributions to this Specification are made under the terms and conditions set forth in Open Web Foundation Contributor License Agreement ("OWF CLA 1.0") ("Contribution License") by:

**OCP OAI Subgroup**

Usage of this Specification is governed by the terms and conditions set forth in the Open Web Foundation Final Specification Agreement ("OWFa 1.0").

Note: The following clarifications, which distinguish technology licensed in the Contribution License and/or Specification License from those technologies merely referenced (but not licensed), were accepted by the Incubation Committee of the OCP:

None.

NOTWITHSTANDING THE FOREGOING LICENSES, THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN, THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO, OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION, INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 2. Acknowledgment

We want to acknowledge all the OCP OAI Workstream members for their contributions to this specification: The incredible collaboration between customers, accelerator manufacturers, system developers, and industry partners shows how Open Compute develops industry-standard form factors and specifications that benefit all its members.

We would especially like to thank Google, H3C, Inspur, Intel, Meta, and Wiwynn for their extra efforts in putting this specification together.

# 3. Introduction and Scope

Open Accelerator Infrastructure (OAI) is an initiative within the OCP Server Project to define a modular, interoperable architecture for systems targeting Machine Learning, Deep Learning, and High-Performance Computing workloads. Beginning with the OCP Accelerator Modules (OAI-**OAM**), OAI defines the logical and physical attributes of all the basic building blocks of an accelerator system design.

A standard way to connect this Open Accelerator Infrastructure to a CPU Box in a rack is shown in Figure 1.

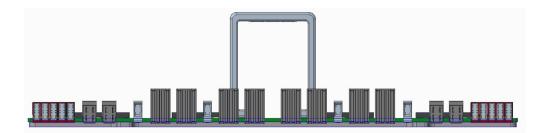

Figure 1 OAI as a disaggregated compute for AI in a Rack.

The Universal Baseboard (UBB) specification is the next step in defining a complete solution for this accelerator infrastructure, leveraging the progress in defining the OAM module and carrying forward the goals of openness and modularity.

The Open Accelerator Infrastructure will be composed of these base building blocks:

- OAI Power Distribution (OAI-PDB): The translation between Rack Power to UBB module power needs.

- OAI Host Interface (OAI-HIB): The HIB provides the interface links between the UBB and head node(s).

- OAI Security, Control, and Management (OAI-SCM): This module provides OAI management, power sequencing, and security.

- OAI Universal Baseboard (OAI-UBB): The UBB Baseboard supports 8 OAM modules in various fabric and interconnects topologies.

- OCP Accelerator Module (OAI-OAM): Specification 1.0 defines the mezzanine module accelerator.

- OAI Expansion (Scale-out) Beyond UBB (OAI-**Expansion**): Specifications describe connections between multiple OAI systems in the same rack or across different racks.

- OAI-Tray: The tray provides mechanical support to adapt various UBBs to both 19" and 21" Chassis and Racks

- OAI-Chassis: This chapter discusses both air-cooled and liquid-cooled implementations.

Specifications for each component will cover logic, power, mechanical, connector interfaces, and thermal infrastructure definitions to ensure interoperability between all the OAI elements.

These elements and their interactions are represented in figure 2.

Figure 2 OAI building blocks

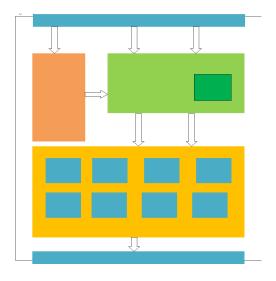

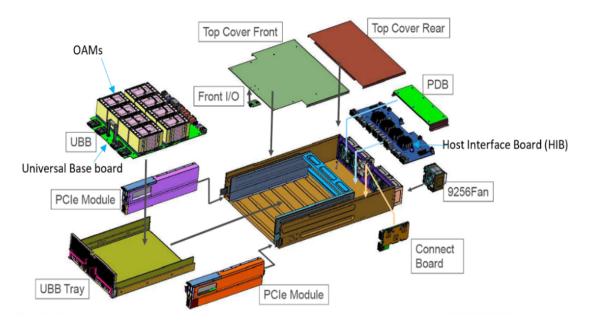

The figure below shows an example system from Inspur as a composite of various OAI building blocks.

Figure 3 Example OAI System Building Blocks

# 4. Universal Baseboard (OAI-UBB) High-level Description

The Universal Baseboard is modular and flexible in supporting current and future OAM modules and providing maximum design flexibility for conceivable system designs. The UBB supports 8 OAM modules, but the board has been engineered to help comprehensive options of interconnecting fabrics and topologies, power domains, TDP's, cooling solutions, and scale-out options. While the board is optimized for a few standard configurations and released OAM modules, great care was taken to accommodate future trends and customer needs.

The Universal Based Board (UBB) is a building block that supports:

| OAM Support                                | <ul> <li>Various interconnect topologies for the 8 OAMs</li> <li>Air or liquid cooling</li> <li>OAM powered by 12V nominal up to 350W (*)</li> <li>OAM powered by 54V/48V nominal up to 700W (*)</li> <li>One x16 host interface per OAM</li> </ul>                                                                                                         |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface to HIB (Host<br>Interface Board) | <ul> <li>8 x16 connectors for host interface connections (one per OAM)</li> <li>Each Host Interface up to x16 lanes (for example, PCIe Gen4)</li> <li>Support for PCIe Gen5 and other future host interfaces</li> <li>Power: 12V, 54V, 12V standby, etc.</li> <li>Sideband signals: I2C, Reset, Reference clocks, JTAG, Power management, et al.</li> </ul> |

| Scale-out Capabilities                     | <ul> <li>QSFP-DD connectors for scale-out interconnect**</li> <li>Exposed from UBB to the exterior of the UBB Tray/System Chassis</li> </ul>                                                                                                                                                                                                                |

| Electrical<br>Interoperability             | <ul> <li>The current UBB reference design supports SERDES links up to 32 Gbps NRZ and up to 112 Gbps PAM4</li> <li>Two Micro USB connectors are exposed from the UBB to the exterior of the chassis for debugging (UART to USB)</li> </ul>                                                                                                                  |

| Mechanical<br>Interoperability             | <ul> <li>PCB dimensions: 417mm wide x 585mm long</li> <li>Supports both 19" and 21" rack chassis infrastructures</li> <li>Defined mounting hole sizes and locations</li> </ul>                                                                                                                                                                              |

Table 1 Universal Based Board (UBB) is a building block

#### Note:

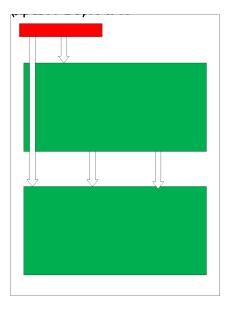

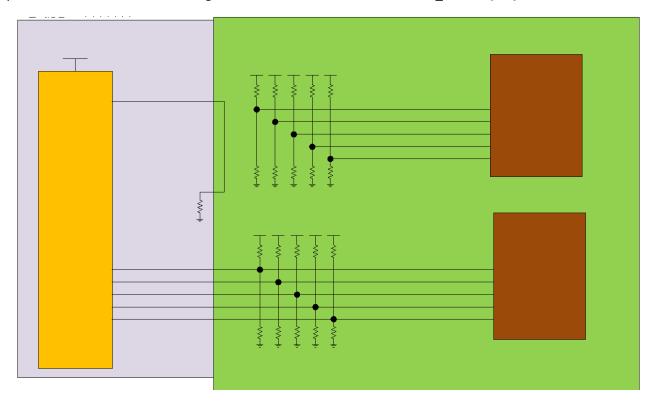

Figure 2 shows the major physical features of the UBB board. In red, you can see power delivery connections to the OAM module. In yellow, you can follow the Host interface, clock, and SCM signals to the OAM module, and in green, you can see scale-out (SERDES) interconnect from the OAM module to external connectors.

<sup>\*</sup> Different UBB designs may have different power support. Check UBB providers for specific product spec.

<sup>\*\*</sup>Number of QSFP-DD connectors is flexible, based on different UBB designs.

**Figure 4 Example UBB System Building Blocks**

Figure 5 Universal Reference Base Board (UBB)

# 5. Input and Output Interfaces

The UBB board is the carrier board that houses the 8 OAM modules, and it defines five primary interfaces to other boards in a complete system design:

- 1 OAM Interface: Interface to the Open Accelerator Modules

- 2 Host Fabric interface: Required interface to host(s) via PCIe or other fabric. The interface fabric is routed to the Host Interface Board where it connects to either a host node integrated within the same chassis or a disaggregated host node.

- 3 Scale-out interface: Optional interface allows multiple UBB boards to connect through QSFP-DD connectors to external switches or node-to-node.

- 4 Miscellaneous Signal Interface: SMBus, USB, Clocks, sideband signals provided by the Host Interface board.

- 5 Input Power Interface 54V/48V, 12V, and 3.3V Aux inputs to the UBB.

#### 5.1. OAM Interconnect Interface

As outlined in the OAM design specification, each OAM has up to eight x16 interconnect links. Each OAM to OAM connection can support different interconnect topologies based on how many links are supported by the specific OAM populated on the UBB.

Please refer to Section 7 for more details on the supported UBB interconnect topologies and OAM Design Specification for pin-out and accelerator module information.

Figure 6 UBB Host and Expansion (scale-out) Interfaces

## 5.2. Host Fabric Interface

This section describes the host interface to the HIB board, including supported fabrics and speeds.

## 5.2.1. Host Interface: High-speed interface

There are eight x16 SerDes links dedicated for host interface connections. Each OAM module on the UBB routes an x16 link to a dedicated ExaMAX connector (shown in Figure 3) which connects to the Host Interface Board.

Different implementations of the Host Interface Board provide customized topologies that allow the UBB to interface to a single host node or multiple hosts in various configurations. System designs can also support either integrated head nodes in the same chassis as the UBB or disaggregated head nodes, which cable to a separate UBB chassis within the rack.

The specification supports industry-standard host protocols such as PCIe Gen5, CXL, Infinity Fabric, and other alternate protocols. The UBB has space allocated for re-timers that may be needed to support specific protocols or configurations needed with different OAM and system designs.

#### 5.2.2. Pin list

A detailed pinout is in section 6.2.1

#### 5.3. Scale-Out Interface

The UBB uses QFSP-DD connectors to scale-out topologies that connect multiple UBB boards through high-speed cables. The number of QSFP-DD connectors varies based on different designs.

## 5.3.1. High-speed support

The QSFP-DD connectors are exposed on the exterior of the UBB tray and system chassis to allow connections to other UBB systems. The QSFP-DD links can be through passive or active copper cables.

OAI UBB reference board supports SerDes data rates up to 112Gbps PAM4. In addition, to support future configurations, space for re-timers has been allocated on the UBB board while SI studies against the various system and cable configurations.

#### 5.3.2. I2C

An I2C interface is included on each QSFP-DD connector to enable cable re-driver tuning and FRU access.

#### 5.3.3. Pin list

Refer to section 6.2.1

# 5.4. Miscellaneous Signal Interface

The UBB also receives necessary ancillary signals from the host interface board that defines security, control, and board management.

## 5.4.1. Clock and I2C Signals

The UBB receives its primary clock, AUX clock, downstream clock from the HIB. Please refer to section 6.1.1 for details.

## 5.4.2. Board management

There are I2C, JTAG, UART for UBB management.

• I2C is used to read OAM information, status, and UBB FRU.

- The host node controls OAM Reset through HIB CPLD to UBB CPLD.

- JTAG is for debugging and FW upgrades.

- UART is used for OAM debug.

#### 5.4.3. Power management

There are PWREN, PWROK, PWRBRK#, thermtrip# signals for power management.

- PWREN: UBB power ready assert OAM power enable.

- PWROK: Indicates OAM power is stable and asserts PWROK to CPLD

- PWRBRK#: There are two sources to trigger PWRBRK#. One is from BMC, and the other is from PSU alert

- Thermtrip#: it indicates OAM silicon has reached an elevated temperature. OAM will power off itself when thermtrip# is triggered. UBB may or may not shut down the entire board. It depends on the different system design requirements.

- UBB Power Ready (UBB\_PWR\_READY): Assert UBB\_PWR\_READY to notice BMC on HIB when all UBB powers are ready.

# 5.5. Input Power Interface

The UBB supports two OAM power types: 54V/48V OAM modules with TDPs up to 700W and 12V OAMs with TDPs up to 350W. A group of connectors supplies DC Power for the UBB on the edge of the board.

**Figure 7 Input Power connectors Placement**

There are four dedicated 54V/48V connectors delivering power from the HIB to the UBB. In addition, two connectors provide 12V power to the OAMs and other UBB components from the host interface board (HIB). One of the 12V power sources is used to power PCIe Retimers, SerDes Retimers, and the 3.3 voltage converter to the QSFP-DD connectors.

3.3V Auxiliary is used to power the CPLDs and other board management components during the DC power off stage.

UBB is designed to support different rack infrastructures and form factors and interface to different system-specific HIB and PDB implementations that support bus bar or discrete power supply solutions. A typical implement is below:

Figure 8 OAI Reference UBB power Delivery Diagram

#### 5.5.1. UBB System Power

UBB is part of the OAI system infrastructure, which supports two distinct power architectures.

One is centralized power in the rack with a busbar, often energized by an in-rack power shelf with several 54V/48V PSUs.

The other method utilizes PSUs integrated into the individual OAI system chassis itself. The PSU's input is from an AC supply, and its output is 54V or 12V. For example, 54V 3000W Platinum PSUs with 3+3 redundancy is one known OAI system implementation.

Please refer to Section 6.2 for the power connector pin list.

## 5.5.2. 54V/48V based OAM power input

Each OAM has an isolated source from 54v/48v through a dedicated hot-swap controller(OAI-PDB power distributed board). The system provider who designs the OAI system shall implement bulk capacitors to support OAM 54V/48V power rails to support OAM EDP. The implementation shall be at the HIB power connectors' side. Please refer to section 5.5.4 for detailed excursion power support.

The following table summarizes the voltage range UBB supports.

|                   | Minimum | Nominal    | Maximum |

|-------------------|---------|------------|---------|

| Operating voltage | 40.0V   | 48.0/54.0V | 59.5V   |

Table 2 UBB input voltage range

The recommended range includes DC level, noise, and other transients. The input rails must remain within 40 to 59.5v.

Although specific UBB has a particular OAM TDP support target based on design, UBB could support up to 700W TDP OAM. The continuous current specification for nominal input voltages between 48.0V and 54.0V can use linear interpolation to approximate.

| Specification         | Voltage(nominal) | Maximum Value | Moving Average |

|-----------------------|------------------|---------------|----------------|

| Input 54V             | 54.0V            | 103.7A        | continuous     |

| Input 48V             | 48.0V            | 116.7A        | continuous     |

| Total baseboard power | 48.0V to 54.0V   | 5600W         | continuous     |

Table 3 UBB(up to 700W OAM) input continuous current specifications

UBB system provider shall check with OAM vendor to get detailed excursion support requirements and apply design accordingly. OAI UBB reference boards support OAM's excursion design power (EDP) of 1.6x TDP (700W based on 48/54V) for a 2ms duration.

| Voltage | EDP      | Current *               | Duration |

|---------|----------|-------------------------|----------|

|         | 2x TDP   | 200%*103.7A(or 116.7A)  | <= 20us  |

| 54V or  | 1.6x TDP | 160%*103.7A(or 116.7A)  | <= 2ms   |

| 48V     | 1.5x TDP | 150%* 103.7A(or 116.7A) | <= 5ms   |

|         | 1.2x TDP | 120%*103.7A(or 116.7A)  | <= 10ms  |

|         | 1.1x TDP | 110%*103.7A(or 116.7A)  | <= 20ms  |

Table 4 UBB(up to 700W OAM) EDP support example

## 5.5.3. 12V based OAM Power input

The 12V input to the UBB could support an EDP of 1.5x for a 5ms duration. The UBB shall provide an isolated 12V rail to each OAM through dedicated E-fuses on the boards. These E-fuses have over current protection and prevent OAM modules from being damaged or affected by over current failures.

The 12V pin assignment is in the UBB spec package.

The following table summarizes the voltage range UBB supports.

|                   | Minimum | Nominal             | Maximum |

|-------------------|---------|---------------------|---------|

| Operating voltage | 11.0V   | 12.2V (11.6V~12.8V) | 13.2V   |

Table 5 UBB operation voltage range

Input electrical design peak specifications are based on nominal voltages, with the continuous current specifications shown below. Linear interpolation can be used to approximate the continuous current specification for nominal input voltages 12V.

| Specification         | Voltage(nominal) | Maximum Value | Moving Average |

|-----------------------|------------------|---------------|----------------|

| Input 12V             | 12.2V            | 230A          | continuous     |

| Total baseboard power | 12.2V            | 2800W         | continuous     |

Table 6 UBB input continuous current specifications

UBB system provider shall check with OAM vendor to get detailed excursion support requirements and apply design accordingly. OAI UBB reference boards support OAM's excursion design power (EDP) of 1.6x TDP(350w) based on 12V for a 2ms duration.

| Voltage | EDP      | Current * | Duration |

|---------|----------|-----------|----------|

|         | 2x TDP   | 200%*230A | <= 20us  |

|         | 1.6x TDP | 160%*230A | <= 2ms   |

| 12V     |          |           |          |

|  | 1.5x TDP | 150%* *230A | <= 5ms  |

|--|----------|-------------|---------|

|  | 1.2x TDP | 120%**230A  | <= 10ms |

|  | 1.1x TDP | 110%**230A  | <= 20ms |

Table 7 UBB(up to 350w 12v based OAM) EDP support example

## **5.5.4. OAM Excursion Power Support**

This section describes the 12V/54V power design guide based on the UBB reference system.

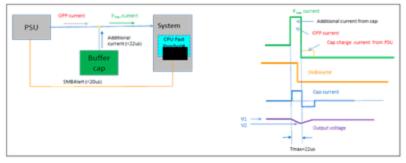

The figure below for reference is based on the peak current requirement to calculate Cmin capacitance for the microsecond(uS).

The total required Min buffer capacitance to support P<sub>max</sub> can be calculated as follows:

$$C_{\min}(\mu F) = 2 \times (P_{\max} - P_{opp}) \cdot \frac{T_{\max}(\mu s)}{V_{1}^{2} - V_{2}^{2}}$$

Figure 9 Cmin calculation for OAM peak current

- Cmin: Min buffer cap size assuming PSU(s) has OuF output capacitance and OuF on the baseboard power rail.

- Pmax: the max system power due to CPU Pmax virus condition.

- Popp: the PSU minimum OPP power level, and it is always set above system power budget corresponding with CPU's Pmax.app

- Tmax: the throttle time delay after the system power exceeds the pre-defined power threshold.

- V1 and V2: The PSU output voltage levels at the beginning and the end of the Pmax time interval (Tmax)

The table is an example for 54V/12V power at 2x EDP 20us calculation result based on reference UBB design. The 54V OAM 700W EDP with 20us duration is about 66uF of Cmin, and the 12V OAM 350W EDP with 20us duration is about 699uF of Cmin. The designer should trade off your PCB space and cost to provide a VR/Cap solution for peak power requirements.

| 700W EDP / 54V OAM               |      |

|----------------------------------|------|

| Cmin(uF) =                       | 66   |

| P_EDP(2x TDP) =                  | 1400 |

| P_TDP =                          | 700  |

| Tmax(uS) =                       | 20   |

| V1(54V_Busbar Vmin spec, -10%) = | 48.6 |

| V2(OAM Vmin spec) =              | 44   |

| 350W EDP / 12V OAM            |        |  |

|-------------------------------|--------|--|

| Cmin(uF) =                    | 699    |  |

| P_EDP(2x TDP) =               | 700    |  |

| P_TDP =                       | 350    |  |

| Tmax(uS) =                    | 20     |  |

| V1(12.5V_VR Vmin spec, -5%) = | 11.875 |  |

| V2(OAM Vmin spec) =           | 11     |  |

Table 8 Cmin requirement at 2x EDP 20us

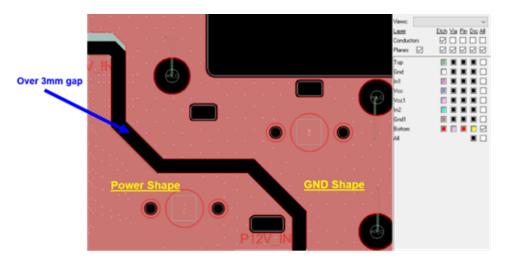

# 5.6. 40V ~ 59.5V power layout guidance

Manufacturing defects can result in shorts or faults across large voltage differentials. This risk needs to address due to the high voltages on the UBB.

Industry safety standards (IEC CDV 62368) require additional safeguards (i.e., creepage/ clearance distances, access restrictions, et al.) for systems with voltages that exceed 60V. Voltage differentials of less than 60Vdc are classified as ES1 voltage sources. While ES1 systems do not require explicit safety safeguards, the guidelines below will minimize the risk of a fault that could cause high energy dissipation or fire.

| Layout Recommendations before Hot Swap | Minimum spacing between conductors with   |

|----------------------------------------|-------------------------------------------|

| Controller / Fuse                      | high potential differences >40V           |

| Internal Layer                         | 25 mils (0.64mm)                          |

| External Layer                         | 120 mils (3.0mm)                          |

| Z-Axis                                 | 17 mils (0.43mm) spacing or 3-ply prepreg |

| Layout Recommendations after Hot Swap  | Minimum spacing between conductors with   |

| Controller / Fuse                      | high potential differences >40V           |

| Internal Layer                         | 25 mils (0.64mm)                          |

| External Layer                         | 60 mils (1.5mm)                           |

| Z-Axis                                 | 3 mils (0.076mm)                          |

Table 9 40V ~ 59.5V layout guidance

Exceptions may be necessary due to the inherent spacing of components and should use DFMEA to evaluate thoroughly on a case-by-case basis.

Good power and ground isolation for an external layer on the UBB are below.

Figure 10 power and GND isolation

# 6. UBB Electrical Specification

This chapter describes details of the UBB electrical design.

# 6.1. Board Architecture specification

The OAI- UBB boards will share a standard hardware architecture definition for various design areas such as Clock distribution, Power Sequence Control, Telemetry, I2C, and GPIO assignments. The standard hardware specification intends to have a single Firmware and Software definition that can cover all different designs and to re-use the hardware solutions as much as possible across the other products.

The typical hardware architecture components include the following definitions.

- Power Delivery

- Clock Distribution

- I2C Interconnectivity

- Power and Reset control

- Power and Reset Sequence

- GPIO definition

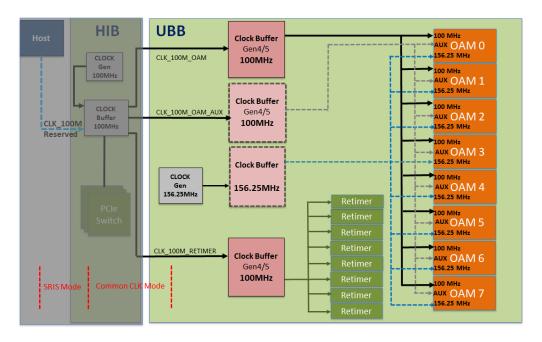

#### 6.1.1. System Clock Architecture

Host to HIB will run in SRIS mode. HIB to UBB will be standard clock mode. SRIS also supports Spread-Spectrum Clocking (SSC) for EMC/ EMI.

Figure 11 OAI Reference UBB clock diagram

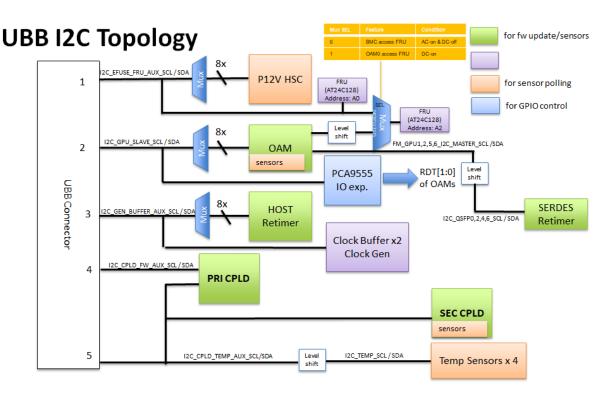

#### 6.1.2. I2C architecture

There are 5 I2C buses to take bus traffic, as illustrated in the diagram below.

Bus1 is for 12V HSC sensor polling.

Bus2 is for OAM sensor information and FW update. PCA9555 IO expander with GPIO control is also on this bus.

Open Accelerator Infrastructure – Universal Baseboard Design Specification v1.5

Bus3 connects SERDES clock gen/ clk buffer as well as retimers.

Bus4 is for scaling out PHY FW update and sensors.

Bus5 is for UBB sensor readings and UBB CPLD FW update.

There's 2 FRU EEPROM on the UBB board. FRU 0 is dedicated to BMC, and FRU 1 is shared with BMC and OAM #0. Refer to section 10.6 for detail.

Below is how the UBB I2C pull-up resistor calculate. Each board designer has to calculate the pull-up time they need.

The minimum resistance calculation as

$$R_p(min)=(V_{cc}-V_{OL}(max))/I_{OL}$$

$V_{cc}$  is the bus voltage,  $V_{OL}(max)$  is the maximum voltage that can read as logic-low, and the maximum current that the pins can sink when at or below  $V_{OL}$ .

The maximum resistance calculation as:

$$R_{\rm p}({\rm max}) = t_{\rm T}/(0.8473 {\rm x} C_{\rm b})$$

$t_{T}$  is the maximum allowed rise time of the bus, and  $C_{b}$  is the total bus capacitance.

Figure 12 I2C/SMBus Block Diagram

#### 6.1.3. Power control

The UBB provides 12V and 54V/48V to 8x OAMs. The 12V is from the HIB power connector (P12V\_1 and P12V\_2) through eFuse (ex: MP5023) control. And the 54V/48V power is directly connected from the HIB power connector (P54\_0, P54\_1, P54\_2, and P54\_3).

The management device of HIB controls all voltage power on/off through the I2C bus to CPLD. The UBB provides the 12V power over 2400W (8x 300W) and 54V/48V over 5600W (8x700W). Therefore, CPLD will control all OAM power enabled to do the time slot for series power-on. The duration of the time slot will update in the next version.

#### 6.1.4. Reset

The following figure shows the UBB reset diagram from the HIB management device (ex, BMC) to the UBB device via CPLD. The I2C bus of the HIB setting to CPLD can control all device reset. UBB onboard device includes OAM, OAM uplink serdes retimer, and OAM scale-out serdes PHY retimer.

Below is each signal naming function:

OAM\_PERST\_[7:0]#: OAM up-link serdes reset signal from HIB via CPLD at the OAI system or host power-on reset.

OAM\_WARMRST\_[7:0]#: OAM warm reset signal from HIB via CPLD at the OAI system reboot or after firmware update.

RETIMER\_PERST\_[7:0]\_A/B#: OAM up-link serdes Retimer-A/B device reset signal from HIB via CPLD.

SERDES\_RESET\_[7:0]#: OAM expansion serdes PHY retimer device reset signal from HIB via CPLD.

Figure 13 UBB Reset signals diagram

# 6.1.5. Power Diagram

Figure 14 Power Control Block Diagram

# **6.1.6. Strap pins**

#### 6.1.6.1. **Module ID**

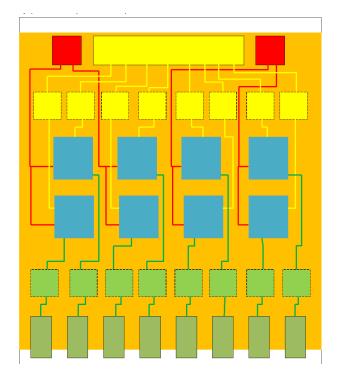

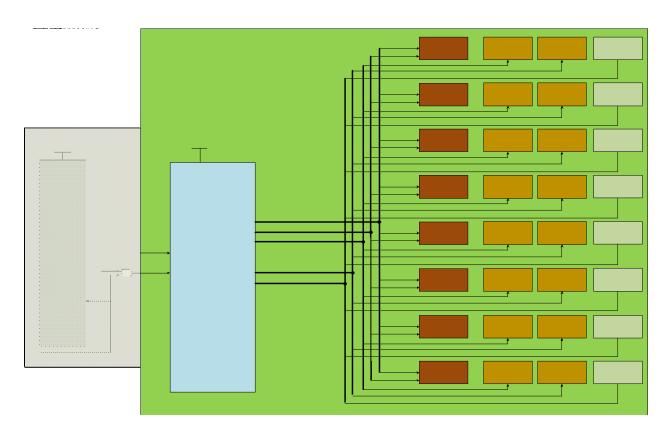

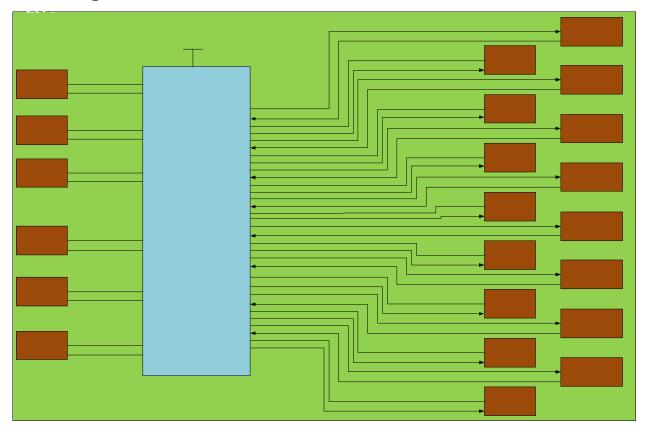

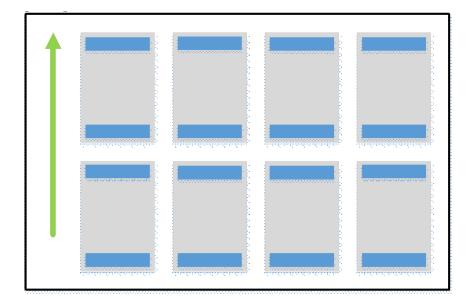

The following figure shows the MODULE\_ID[4:0] strapping for physical orientation of modules when 8 interconnected Accelerators used.

Figure 15 Required MODULE\_ID[4:0] assignments for baseboards with 8 interconnected modules

Detail port to port assignment is based on system placement and routing length. Module to module interconnect may decrease to 4 ports if the module only supports 4. Module to module interconnect link may only utilize 8 lanes if the module defines 8 lanes per link.

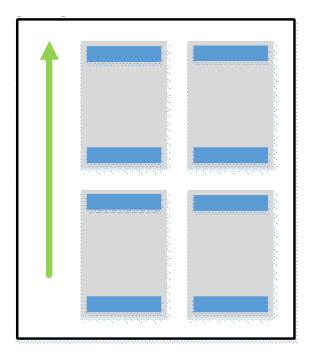

The following Figure shows the required MODULE\_ID[4:0] assignments when only 4 modules are connected as two rows of two.

Figure 16 Module\_ID[4:0] assignments when four only in two rows of two

MODULE\_ID can be used as the I2C address strap pins if needed.

| OAM  | Module ID |

|------|-----------|

| OAM0 | 00000     |

| OAM1 | 00001     |

| OAM2 | 00010 |

|------|-------|

| OAM3 | 00011 |

| OAM4 | 00100 |

| OAM5 | 00101 |

| OAM6 | 00110 |

| OAM7 | 00111 |

Table 10 MODULE\_ID

#### 6.1.6.2. **Link\_Config[4:0]**

The 5 link configuration strapping bits are pulled up on modules that use them. These bits are strapped to the ground on the baseboard to select logic 0 or left floating to select logic 1. Some OAMs use these LINK\_CONFIG[4:0] strapping bits to determine the interconnect topology for the links between modules and determine the protocol of the "P" Link. Refer to Chapter 7.2 for details.

#### 6.1.6.3. **PE\_BIF[1:0]**

x16 Host Interface Bifurcation Configuration. This module output informs the host if it needs to bifurcate the PCIe interface to the module.

00 = one x16 PCIe host interface

01 = bifurcation into two x8 PCle host interfaces

10 = bifurcation into four x4 PCIe host interfaces

11 = reserved

#### 6.1.7. Debug interface

There are two OAM debug interfaces on UBB, one is JTAG, and the other is the UART interface. UART supports both micro USB local access and BMC's remote debugging feature. BMC can access 8 OAM UART output at a time.

There is also one debug header on UBB to support OAM debug through the dongle.

Below are JTAG, UART, and debug header diagrams.

#### 6.1.8. JTAG Interface

Figure 17 JTAG diagram

#### JTAG Truth Table:

#### MUX\_A:

| SELECTION | DESCRIPTION        | REMARK  |

|-----------|--------------------|---------|

| LOW       | PRI CPLD FW UPDATE |         |

| HIGH      | GO TO SEC CPLD     | Default |

#### MUX B:

| SELECTION | DESCRIPTION     | REMARK  |

|-----------|-----------------|---------|

| LOW       | UPDATE SEC CPLD |         |

| HIGH      | OAM JTAG CHAIN  | Default |

#### MUX\_C:

| SELECTION | DESCRIPTION      | REMARK  |

|-----------|------------------|---------|

| LOW       | UPDATE BY HEADER |         |

| HIGH      | UPDATE BY BMC    | Default |

#### MUX\_D:

| SELECTION | DESCRIPTION      | REMARK  |

|-----------|------------------|---------|

| LOW       | UPDATE BY HEADER |         |

| HIGH      | UPDATE BY BMC    | Default |

**Table 11 JTAG Truth Table**

#### 6.1.9. **UART**

There are two interfaces, micro USB and BMC, for OAM UART access through USB Mux. The USB Hub illustrate below. Micro USB takes priority if it is plugged. BMC be notified once a micro USB connector is plugged through USB\_Mux\_Sel signals on HIF\_5 connector N8, O8 pins.

BMC console can see 8 OAM UART at a time.

Figure 18 UART Diagram

#### 6.1.10. Debug Header

A debug header is combined with proprietary debug interfaces from different OAM vendors by using OAM test pins. The debug header is optional in UBB spec. The one used in the OAI UBB reference design is Molex 501190-4017 with pin definition below:

Figure 19 UBB reference board debug header

| 2  | OAM_TEST_0          | NC         | 1  |

|----|---------------------|------------|----|

| 4  | OAM_TEST_1          | NC         | 3  |

| 6  | OAM_TEST_2          | NC         | 5  |

| 8  | OAM_TEST_3          | NC         | 7  |

| 10 | OAM_TEST_4          | NC         | 9  |

| 12 | OAM_TEST_5          | NC         | 11 |

| 14 | OAM_TEST_6          | GND        | 13 |

| 16 | OAM_TEST_7          | GND        | 15 |

| 18 | OAM_TEST_8          | GND        | 17 |

| 20 | OAM_TEST_9          | GND        | 19 |

| 22 | OAM_TEST_10         | GND        | 21 |

| 24 | OAM_TEST_11         | JTAG_HOOK0 | 23 |

| 26 | OAM_TEST_12         | JTAG_HOOK6 | 25 |

| 28 | OAM_TEST_13         | JTAG_HOOK7 | 27 |

| 30 | OAM_TEST_14         | GND        | 29 |

| 32 | GND                 | JTAG_TCK   | 31 |

| 34 | NC                  | JTAG_TDO   | 33 |

| 36 | VREF                | JTAG_TRST  | 35 |

| 38 | NC                  | JTAG_TDI   | 37 |

| 40 | DEBUG_PRESENT<br>_N | JTAG_TMS   | 39 |

Table 12 UBB debug header pin definition

# 6.1.11. UBB Power sequence

UBB board power sequence diagrams are below.

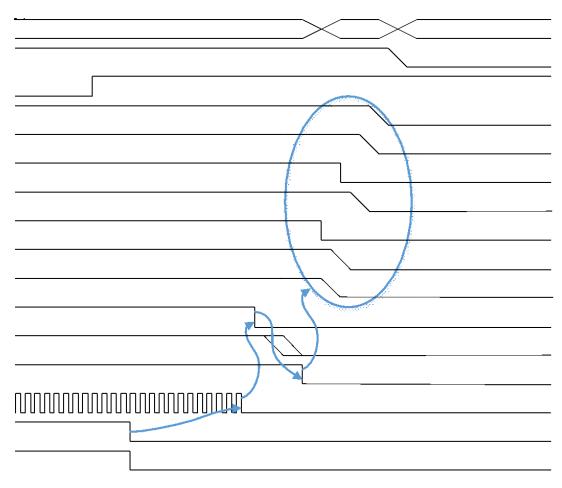

Figure 20 UBB Power-on sequence

Figure 21 UBB Power-down sequence

#### Notes:

- 1. All voltages on the UBB must be within specification before MODULE\_ENABLE is asserted.

- 2. HOST/PHY\_RETIMER\_VR depends on the system provider's design to be in the UBB design or not.

- 3. The MODULE\_ENABLE is the UBB power good indication signal.

- 4. As the voltage planes on the UBB ramp up, the reference clocks from the UBB will begin to run.

- 5. After all the voltages on the module are within specification, the module asserts MODULE\_PWRGD to the UBB.

- 6. At least 100ms after MODULE\_PWRGD assertion, the UBB will de-assert the PCIe reset signal(PERST#) to the module.

- 7. The optional WARMRST# signal de-asserts simultaneously or later than the PERST# signal is de-asserted.

- 8. Using clock buffer enables the pin to control reference clock disable earlier than P3V3\_VR\_EN.

- 9. Clock buffer enables pins to connect to CPLD.

- 10. After MODULE\_ENABLE de-asserted, if Module\_PWRGD doesn't de-asserted in 100ms, shut down all power.

- 11. UBB\_PWR\_ON\_N is monitored by CPLD on HIB

#### 6.1.12. FRU

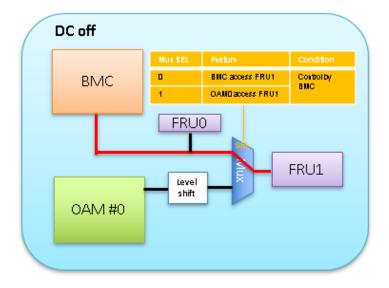

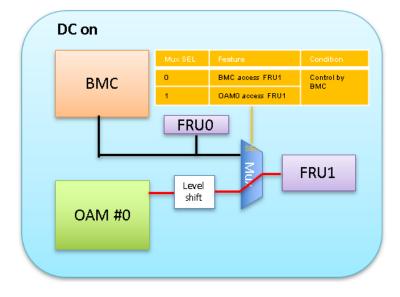

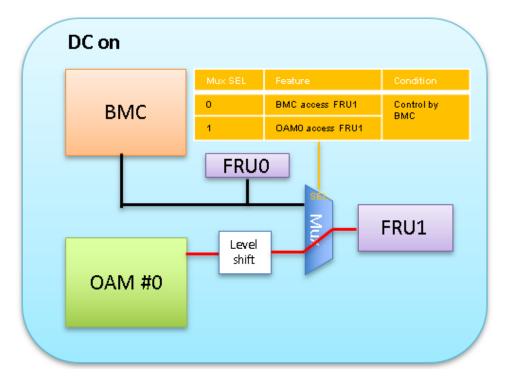

Please refer to section 10.3 for detailed FRU format. BMC controls MUX selection via BMC GPIO:

When DC is off, BMC switches FRU1 access to BMC.

When DC is on, BMC switches FRU1 access to OAM0

Figure 22 DC is off, BMC switches FRU1 access to BMC

Figure 23 When DC is on, BMC switches FRU1 access to OAMO

#### Case 1: DC off

- 1. BMC switches MUX to BMC access.

- 2. If FRU0 is changed, copy FRU0 to FRU1

#### Case 2: DC on

- 1. BMC switches MUX to OAM #0.

- 2. OAM #0 to update link topology by FRU1.

#### Case 3: OAM reset

- 1. User send OAM to reset command to BMC

- 2. BMC pulls down OAM reset and then switches MUX to BMC.

- 3. If FRU0 is changed, copy FRU0 to FRU1.

- 4. Switch MUX to OAM #0, and then release OAM reset signal.

#### Case 4: User update FRU0

- 1. User updated FRU0 via BMC OOB interface.

- 2. BMC stores these changes in FRU0 and waits for events of DC off or OAM reset.

- 3. DC off: use "Case 1: DC off" above to update FRU1.

- 4. OAM reset: use "Case 3: OAM reset" above to update FRU1.

#### 6.2. UBB Connectors

UBB has 8 6x8 high-density connectors, 16 OAM Mezz connectors, 8 OSFP-DD connectors for scale-out, 4 mechanical guide pins, 4 54V power connectors, 2 12V power connectors (can be repurposed for 54V power delivery, see 6.2.1.4), 2 micro USB UART ports. Details are in the table below.

| Board | Vendor   | Vendor PN         | Description            | Q'ty | Desination | TYPE        | R/V | Solder Type |

|-------|----------|-------------------|------------------------|------|------------|-------------|-----|-------------|

|       | Amphenol | 10131762-101LF    | High Density Connector | 8    | SW         | Receptacle  | RA  | Press-Fit   |

|       | Molex    | 2093111115        | OAM Connector          | 16   | OAM Module | Mirror type | VT  | SMT         |

|       | Amphenol | UE36-A 1070-3000T | QSFP-DD Connector      | 8    | UBB        | Receptacle  | RA  | SMT         |

| UBB   | Amphenol | UE36B 16221-06A5A | QSFP-DD Cage           | 8    | UBB        | Receptacle  | RA  | Press-Fit   |

| UDD   | Amphenol | 10037909-101LF    | Guide Pin              | 4    | UBB        | Receptacle  | RA  | Press-Fit   |

|       | Amphenol | 10028917-001LF    | 54V Connector          | 4    | SW         | Header      | RA  | Press-Fit   |

|       | Amphenol | JX410-xxxx        | 12V Connector          | 2    | SW         | Header      | RA  | Press-Fit   |

|       | ACES     | 59493-0050D-CH1   | Micro USB Connector    | 2    | UBB        |             | RA  | SMT         |

Table 13 UBB connector list

Note: For 12V Connector, the last 5 digits changes are based on system design requirements.

#### 6.2.11. UBB Connector pin list

This chapter describes connectors including Host Interface, 12V power, 54V power, QSFP-DD, debug header.

#### 6.2.11.1. **QSFP-DD connector pin list**

Each QSFP-DD Tx and Rx is AC-coupled 100 ohm differential lines that shout be terminated with 100 ohms differentially at the Host ASIC(SerDes). The AC coupling is inside the QSFP-DD module and not required on the Host board.

The QSFP-DD low-speed electrical specifications are in the below table. This specification ensures compatibility between host bus masters and the I2C interface.

| Parameter        | Symbol | Min     | Max     | Unit | Condition                                                          |

|------------------|--------|---------|---------|------|--------------------------------------------------------------------|

| SCL and SDA      | VOL    | 0       | 0.4     | V    | IOL(max)=3mA for fast mode, 20ma for Fast-mode plus                |

| CCL and CDA      | VIL    | -0.3    | Vcc*0.3 | V    |                                                                    |

| SCL and SDA      | VIH    | VCC*0.7 | Vcc+0.5 | V    |                                                                    |

| InitMode, ResetL | VIL    | -0.3    | 0.8     | V    |                                                                    |

| and ModSelL      | VIH    | 2       | VCC+0.3 | V    |                                                                    |

| 141              | VOL    | 0       | 0.4     | V    | IOL=2.0mA                                                          |

| IntL             | VOH    | VCC-0.5 | VCC+0.3 | V    | 10k ohms pull-up to Host<br>Vcc                                    |

| ModDral          | VOL    | 0       | 0.4     | V    | IOL=2.0mA                                                          |

| ModPrsL          | voн    | VCC-0.5 | VCC+0.3 | V    | ModPrsL can be implemented as a short-circuit to GND on the module |

Table 14 QSFP-DD low-speed electrical specifications

For detailed QSFP-DD information, please refer to "QSFP-DD Hardware Specification for QSFP DOUBLE DENSITY 8X PLUGGABLE TRANSCEIVER – Rev 5.0."

#### QSFP-DD Connector 0~7 pin list (Input, Output are based on UBB side)

All signals direction below are based on the UBB side

| Signal          | UBB<br>Direction<br>POV | Description                                                                                          | Voltage | Total<br>Diff<br>Pins | Total<br>Single<br>Pins |

|-----------------|-------------------------|------------------------------------------------------------------------------------------------------|---------|-----------------------|-------------------------|

| GND             | GND                     | GND                                                                                                  | GND     |                       | 24                      |

| Vcc1            | PWR                     | +3.3V Power supply                                                                                   | 3.3V    |                       | 1                       |

| Vcc2            | PWR                     | 3.3V Power Supply                                                                                    | 3.3V    |                       | 1                       |

| VccTx           | PWR                     | +3.3V Power supply transmitter                                                                       | 3.3V    |                       | 1                       |

| VccTx1          | PWR                     | 3.3V Power Supply                                                                                    | 3.3V    |                       | 1                       |

| VccRx           | PWR                     | +3.3V Power Supply Receiver                                                                          | 3.3V    |                       | 1                       |

| VccRx1          | PWR                     | 3.3V Power Supply                                                                                    | 3.3V    |                       |                         |

| РЕТр/n<br>[8:1] | Output                  | PCIe or equivalent link Transmit differential pairs. OAM module Transmit, QSFP-DD connector Receive. |         | 16                    | 16                      |

| PERp/n<br>[8:1] | Input          | PCIe or equivalent link Receive differential pairs. OAM module Receive, QSFP-DD connector Transmit. |      | 16 | 16 |

|-----------------|----------------|-----------------------------------------------------------------------------------------------------|------|----|----|

| I2C_SLV_<br>D   | Bi-directional | Slave I2C data                                                                                      | 3.3V |    | 1  |

| I2C_SLV_<br>CLK | Output         | Slave I2C clock                                                                                     | 3.3V |    | 1  |

| RESETL          | Output         | QSFP-DD Module Reset                                                                                | 3.3V |    | 1  |

| INTL            | Input          | QSFP-DD Module Interrupt                                                                            | 3.3V |    | 1  |

| MODSELL         | Output         | QSFP-DD Module Select                                                                               | 3.3V |    | 1  |

| MODPRSL         | Input          | QSFP-DD Module Present for inform OAM cable insert or not.                                          | 3.3V |    | 1  |

| INITMODE        | Output         | Initialization mode; In legacy<br>QSFP applications, the<br>InitMode pad is called<br>LPMODE        | 3.3V |    | 1  |

Table 15 QSFP-DD connector 0~7 pin list

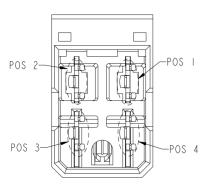

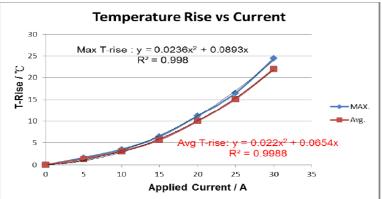

# 6.2.11.2. **54V power connector pin list**

Base on temperature rise under 30°C, 18Amp per contact (POS).

Figure 24 54V power connector

54V power derating

| Applied Current/A                         | 5    | 10   | 15   | 20    | 25    | 30    | 32    |

|-------------------------------------------|------|------|------|-------|-------|-------|-------|

| Max T-rise/°ℂ                             | 1.63 | 3.53 | 6.46 | 11.17 | 16.46 | 24.38 | 29.31 |

| Avg. of Max T-rise/<br>℃ of each sample/℃ | 1.35 | 3.10 | 5.69 | 9.99  | 15.15 | 22.00 | 27.08 |

• The thermal test for the vertical connector, the Max T-rise, is around 12°C, 20A.

### P54V\_0 Pin Definition:

| POS 1 & 2 | 54V_1 | 54V_0 |

|-----------|-------|-------|

| POS 3 & 4 | GND   | GND   |

Table 16 P54V\_0 Pin Definition

### P54V\_1 Pin Definition:

| POS 1 & 2 | 54V_2 | 54V_3 |

|-----------|-------|-------|

| POS 3 & 4 | GND   | GND   |

Table 17 P54V\_1 Pin Definition

### P54V\_2 Pin Definition:

| POS 1 & 2 | 54V_4 | 54V_5 |

|-----------|-------|-------|

| POS 3 & 4 | GND   | GND   |

Table 18 P54V\_2 Pin Definition

P54V\_3 Pin Definition:

| POS 1 & 2 | 54V_7 | 54V_6 |

|-----------|-------|-------|

| POS 3 & 4 | GND   | GND   |

Table 19 P54V\_3 Pin Definition

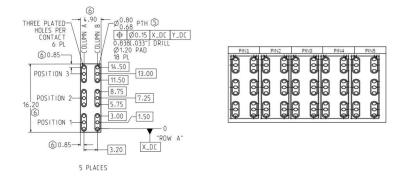

### 6.2.11.3. **12V power connector pin list**

Based on temperature rise under 30°C, 10Amp per contact (POS).

Figure 25 12V power connector pin list

| P12V_<br>0<br>CONN | PIN   | N 1   | PIN   | N 2   | PIN   | N 3   | PIN   | ۱4    | PIN   | N 5   |

|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                    | COLM  | COLM  | COLM  | COLM  | COLMN | COLMN | COLM  | COLM  | COLM  | COLM  |

|                    | NΑ    | N B   | NA    | N B   | Α     | В     | NΑ    | N B   | NΑ    | N B   |

| POS3               | P12V_ |

| 1 000              | VR1   | VR1   | VR1   | VR1   | UBB   | UBB   | VR0   | VR0   | VR0   | VR0   |

| POS2               | P12V_ | P12V_ | GND   | GND   | P12V_ | GND   | GND   | GND   | P12V_ | P12V_ |

| PU32               | VR1   | VR1   | טאט   | טאט   | UBB   | טווט  | טאט   | טאט   | VR0   | VR0   |

| POS1               | GND   |

Table 20 P12V\_0 power connector pin list

| P12V_<br>1<br>CONN | PII          | N 1          | PII          | N 2          | PIN         | N 3         | PIN          | N 4          | PII          | N 5          |

|--------------------|--------------|--------------|--------------|--------------|-------------|-------------|--------------|--------------|--------------|--------------|

|                    | COLMN A      | COLMN B      | COLMN A      | COLMN B      | COLM<br>N A | COLM<br>N B | COLMN A      | COLMN B      | COLMN A      | COLMN B      |

| POS3               | P12V_VR<br>2 | P12V_VR<br>2 | P12V_VR<br>2 | P12V_VR<br>2 | GND         | GND         | P12V_VR<br>3 | P12V_VR<br>3 | P12V_VR<br>3 | P12V_VR<br>3 |

| POS2               | P12V_VR<br>2 | P12V_VR<br>2 | GND          | GND          | GND         | GND         | GND          | GND          | P12V_VR<br>3 | P12V_VR<br>3 |

| POS1               | GND          | GND          | GND          | GND          | GND         | GND         | GND          | GND          | GND          | GND          |

Table 21 P12V\_1 power connector pin list

### 6.2.11.4. **12V** power connector re-purpose for **54V**

12V power connector (JX410-xxxxx) also can be used for 54V applications to support more than 700W OAM. ODM should notice creepage and clearance design (see 11.3 in detail) for this connector. Please refer to the suggestion pin list below:

| P12V<br>CONN | PIN     | N 1     | PIN     | ١2      | PIN     | N 3     | PIN     | ١4      | PIN     | N 5     |

|--------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

|              | COLMN A | COLMN B |

| POS3         | P54V    | P54V    | P54V    | P54V    | NC      | NC      | GND     | GND     | GND     | GND     |

| POS2         | P54V    | P54V    | P54V    | P54V    | NC      | NC      | GND     | GND     | GND     | GND     |

| - 1 | DOC1 | DE 41/ | DE 41/ | DE 4V | DE 4V | NC | NC | CND | CND | CNID | CNID |

|-----|------|--------|--------|-------|-------|----|----|-----|-----|------|------|

| - 1 | POS1 | P54V   | P54V   | P54V  | P54V  | NC | NC | GND | GND | GND  | GND  |

#### 6.2.11.5. Host Interface Connector (HIF) pin list

This chapter describes the Host Interface connector (HIF). There are 8 connectors. The signal direction of HIF0~7 in the table below is based on the UBB side. Detailed pin map is in UBB spec package available on OAI WiKi:

https://www.opencompute.org/wiki/Server/OAI

#### HIF\_0 connector (host interface can be opencapi or others)

High-Speed Connector: (used when it is PCIe interface. For other interfaces, refer to other future section to be provided)

| Signal              | UBB<br>Direction<br>POV | Description                                                                                                | Voltage | Required or<br>Optional | Total<br>Diff<br>Pins | Total<br>Single<br>Pins |

|---------------------|-------------------------|------------------------------------------------------------------------------------------------------------|---------|-------------------------|-----------------------|-------------------------|

| GND                 |                         | GND                                                                                                        |         | Required                |                       | 68                      |

| P3V3_AUX            | Power input             | 3.3V AUX Power for UBB board                                                                               | 3.3V    | Required                |                       | 4                       |

| PETp/n<br>[15:0]    | Output                  | PCIe or equivalent<br>host<br>link Transmit<br>differential pairs.<br>Module Transmit,<br>Host<br>Receive. |         | Required                | 32                    | 32                      |

| PERp/n<br>[15:0]    | Input                   | PCIe or equivalent<br>host<br>link Receive<br>differential<br>pairs. Module<br>Receive,<br>Host Transmit.  |         | Required                | 32                    | 32                      |

| UBB_DETEC<br>T_LOOP |                         | UBB board PRSNT<br>pin. Pull down this<br>pin with a<br>100ohm resistor<br>on the HIB side.                | 3.3V    | Required                |                       | 1                       |

Table 22 HIF\_0 connector pin list

#### HIF\_1 connector (host interface can be opencapi or others)

| Signal | UBB<br>Direction<br>POV | Description | Voltage | Required or Optional | Total<br>Diff<br>Pins | Total<br>Single<br>Pins |

|--------|-------------------------|-------------|---------|----------------------|-----------------------|-------------------------|

| GND    |                         | GND         |         | Required             |                       | 64                      |

<sup>(\*)</sup> Note: UBB\_DETECT\_LOOP on HIF\_0 and HIF\_7 are the same signal. This pin is to inform HIB BMC when UBB is detected. Connect this pin on the UBB side.

| PETp/n<br>[15:0]  | Output         | PCIe or equivalent host<br>link Transmit<br>differential pairs.<br>Module Transmit, Host<br>Receive. |      | Required | 32 | 32 |

|-------------------|----------------|------------------------------------------------------------------------------------------------------|------|----------|----|----|

| PERp/n<br>[15:0]  | Input          | PCIe or equivalent host<br>link Receive differential<br>pairs. Module Receive,<br>Host Transmit.     |      | Required | 32 | 32 |

| UART_SEL<br>_0    | Input          | UART SEL pin                                                                                         | 3.3V | Required |    | 1  |

| UART_SEL<br>_1    | Input          | UART SEL pin                                                                                         | 3.3V | Required |    | 1  |

| UART_SEL<br>_2    | Input          | UART SEL pin                                                                                         | 3.3V | Required |    | 1  |

| UART_MU<br>X_EN_N | Input          | UART MUX enable pin                                                                                  | 3.3V | Required |    | 1  |

| BMC_MDC<br>/MDIO  | Bi-directional | MDC/MDIO signal.                                                                                     |      | Required |    | 2  |

Table 23 HIF\_1 connector pin list

## HIF\_2 connector (host interface can be opencapi or others)

| Signal           | UBB<br>Direction<br>POV | Description                                                                                          | Voltage | Required or<br>Optional | Total<br>Diff<br>Pins | Total<br>Single<br>Pins |

|------------------|-------------------------|------------------------------------------------------------------------------------------------------|---------|-------------------------|-----------------------|-------------------------|

| GND              |                         | GND                                                                                                  |         | Required                |                       | 64                      |

| PETp/n<br>[15:0] | Output                  | PCIe or equivalent host<br>link Transmit<br>differential pairs.<br>Module Transmit, Host<br>Receive. |         | Required                | 32                    | 32                      |

| PERp/n<br>[15:0]                  | Input          | PCIe or equivalent host link Receive differential pairs. Module Receive, Host Transmit. |      | Required | 32 | 32 |

|-----------------------------------|----------------|-----------------------------------------------------------------------------------------|------|----------|----|----|

| CLK_100M_<br>OAM_DP/N             | Input          | PCIe Reference Clock for OAM.<br>100MHz PCIe Gen 4 compliant.                           |      |          | 1  | 2  |

| CLK_100M_<br>RETIMER_D<br>P/N     | Input          | PCIe Reference Clock for retimer.<br>100MHz PCIe Gen 4 compliant.                       |      | Required | 1  | 2  |

| CLK_100M_<br>OAM_AUX<br>_DP/N     | Input          | PCIe Reference Clock for Aux.<br>100MHz PCIe Gen 4 compliant.                           |      | Required | 1  | 2  |