V2 Power Shelf Specification 6600W @ 12.6V DC (2+1) Redundant

Author: Pierluigi Sarti, Technical Lead, Open Rack and Power, Facebook

Author: Samir Kala, Power Engineer, Facebook

Author, Zoh Ebrahimzadeh, Power Engineer, Facebook (RS485 Communication Manual and Digital section)

## Scope

This specification defines the requirement for a 6600W stand-alone V2 Power Shelf, single-voltage 12.6Vdc output, powered from three-phase AC line, hosting three 3300W hot-swappable single-phase power modules. This product is used for IT Systems, for both online and back-up power functions. At the system level, this device will work in conjunction with battery back-up unit (BBU) modules (installed in the same shelf) for power back-up functionality.

# Table of Contents

| 2 | cone |                                                       | 2  |  |

|---|------|-------------------------------------------------------|----|--|

| 1 | •    | verview                                               |    |  |

| 2 | Lic  | ense                                                  | 7  |  |

| 3 | Cor  | mpliance Requirements                                 |    |  |

|   | 3.1  | Safety Certifications, Applicable Documents           | 8  |  |

|   | 3.2  | Immunity Standards, EMC                               | 8  |  |

|   | 3.3  | Industrial Immunity Standards                         | 8  |  |

|   | 3.4  | EMI Compliance & Limits                               | 9  |  |

|   | 3.5  | Environmental Engineering Standards                   | 9  |  |

|   | 3.6  | AC Mains Leakage Current                              | 9  |  |

|   | 3.7  | Restriction of Hazardous Substances (RoHS) Compliance | 9  |  |

| 4 | AC   | AC Input Requirements (Main AC to DC converter)       |    |  |

|   | 4.1  | AC Input Voltage, AC Loss Detection Time              | 9  |  |

|   | 4.2  | Input AC/DC PSU Connector, Fuse, EMI Filter           | 10 |  |

|   | 4.3  | Primary Metal-oxide Semiconductor (MOS) and BULK Caps | 10 |  |

|   | 4.4  | AC Inrush Current, Preferred Topology                 | 11 |  |

|   | 4.5  | AC Hold-up Time                                       | 11 |  |

|   | 4.5  | 1 AC Drop Test                                        | 11 |  |

|   | 4.6  | AC Input Under Voltage Protection                     | 12 |  |

|   | 4.7  | Internal Bias Supply                                  | 12 |  |

|   | 4.8  | Power Factor & THD                                    | 12 |  |

|   | 4.9  | Input AC Surge                                        | 13 |  |

|   | 4.9  | 1 Primary Protection                                  | 13 |  |

|   |      |                                                       |    |  |

|     | 4.9.2 | 2 Isolation Requirements                           | 13 |

|-----|-------|----------------------------------------------------|----|

|     | 4.9.3 | 3 High Potential and Ground Continuity             | 13 |

| 5   | DC (  | Output Requirements (Main Converter)               | 14 |

|     | 5.1   | Output Voltage and Power                           | 14 |

|     | 5.2   | Output Over Current Protection                     | 14 |

| 5.3 |       | Output Over Voltage Protection                     | 14 |

|     | 5.4   | Over Temperature Protection (OTP)                  | 14 |

|     | 5.5   | Capacitive Load                                    | 15 |

|     | 5.6   | Transient Response                                 | 15 |

|     | 5.7   | Output Voltage Ripple and Noise                    | 15 |

|     | 5.8   | Output Turn-on/Turn-off                            | 16 |

|     | 5.8.1 | 1 Power Supply Turn-On Sequence                    | 16 |

|     | 5.9   | Microprocessor Control, Digital Bus, R&D Support   | 19 |

|     | 5.9.1 | 1 Internal Cooling Fan, External Fan Guard         | 22 |

|     | 5.9.2 | 2 Power Supply Efficiency (AC Main Converter)      | 24 |

|     | 5.9.3 | 3 Power Quality                                    | 25 |

|     | 5.9.4 | 4 Stability                                        | 25 |

| 6   | Batte | tery Backup Section (Back-up Converter)            | 26 |

|     | 6.1   | Summary for the Whole Back-up Section Requirements | 26 |

|     | 6.2   | Signal Definitions:                                | 26 |

|     | 6.2.1 | 1 Shelf AC Turn On Sequence                        | 27 |

|     | 6.2.2 | 2 Shelf AC Turn Off Sequence                       | 27 |

|     | 6.2.3 | 3 Backup Sequence                                  | 28 |

|     | 6.2.4 | 4 Battery Test Sequence                            | 29 |

|     | 6.3   | Charge Sequence                                    | 33 |

| 7   | Batte | tery Backup Unit                                   | 33 |

|     | 7.1   | 12Vdc from the PSU to the BBU                      | 33 |

|     | 7.2   | BBU Latched Condition                              | 33 |

|     | 73    | RRII Signals                                       | 33 |

|                                                            | 7.4  | BBU Leakage Current                                               | 34 |

|------------------------------------------------------------|------|-------------------------------------------------------------------|----|

| 8                                                          | Bacl | cup Converter – Step Down                                         | 34 |

|                                                            | 8.1  | DC Input Requirements                                             | 34 |

|                                                            | 8.2  | DC Output Requirements                                            | 35 |

| 9                                                          | Bacl | kup Converter – Step Up                                           | 35 |

|                                                            | 9.1  | DC Input Requirements                                             | 35 |

|                                                            | 9.2  | DC Output Requirements                                            | 36 |

| 10                                                         | Aux  | iliary Converter                                                  | 36 |

|                                                            | 10.1 | DC Input Requirements                                             | 36 |

|                                                            | 10.2 | DC Output Requirements                                            | 37 |

| 11                                                         | Curi | rent Share Functionalities                                        | 37 |

| 12                                                         | Pow  | er Supply Block Diagram                                           | 38 |

| 13                                                         | Env  | ronmental Requirements                                            | 38 |

|                                                            | 13.1 | Vibration & Shock                                                 | 39 |

| 14                                                         | Safe | ty Label                                                          | 39 |

| 15                                                         | Con  | nectors                                                           | 40 |

| 8 8 8 8 8 9 9 9 9 9 10 11 11 11 11 11 11 11 11 11 11 11 11 | 15.1 | 12V Output from the PSU                                           | 40 |

|                                                            | 15.2 | AC and DC Input for the PSU                                       | 40 |

| 16                                                         | Mec  | hanical Requirements                                              | 40 |

|                                                            | 16.1 | Physical Dimensions                                               | 40 |

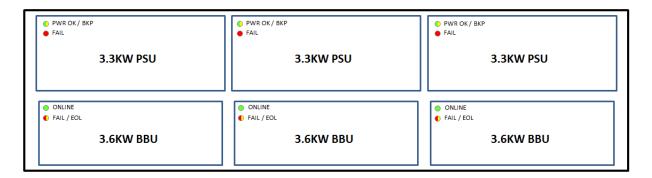

| 17                                                         | LED  | Os, Silkscreen                                                    | 41 |

| 18                                                         | Reli | ability, Quality, Miscellaneous                                   | 43 |

|                                                            | 18.1 | Spec Compliance, Quality FA, Warranty                             | 43 |

|                                                            | 18.2 | Mass Production: First Article Samples                            | 44 |

|                                                            | 18.3 | Mean Time Between Failures Requirements                           | 44 |

|                                                            | 18.4 | Design-rating Guidelines, Design for Test, Design for Manufacture | 44 |

|                                                            | 18.5 | Not Allowed Components                                            | 45 |

|                                                            | 18.6 | Quality Control, Process, Burn-In                                 | 45 |

|                                                            | 18.7 | Packaging                                                         | 46 |

|    | 18.8 | Doci    | umentation                                   | 46 |

|----|------|---------|----------------------------------------------|----|

|    | 18.  | .8.1    | Conformal Coating and Protection             | 47 |

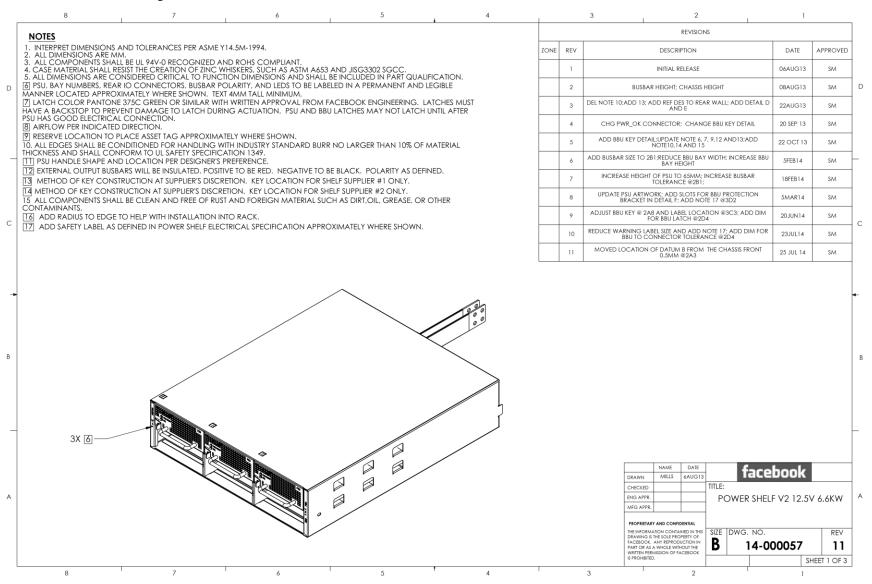

| 19 | V2   | Shelf   | Overview                                     | 48 |

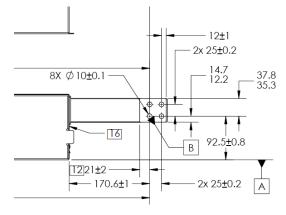

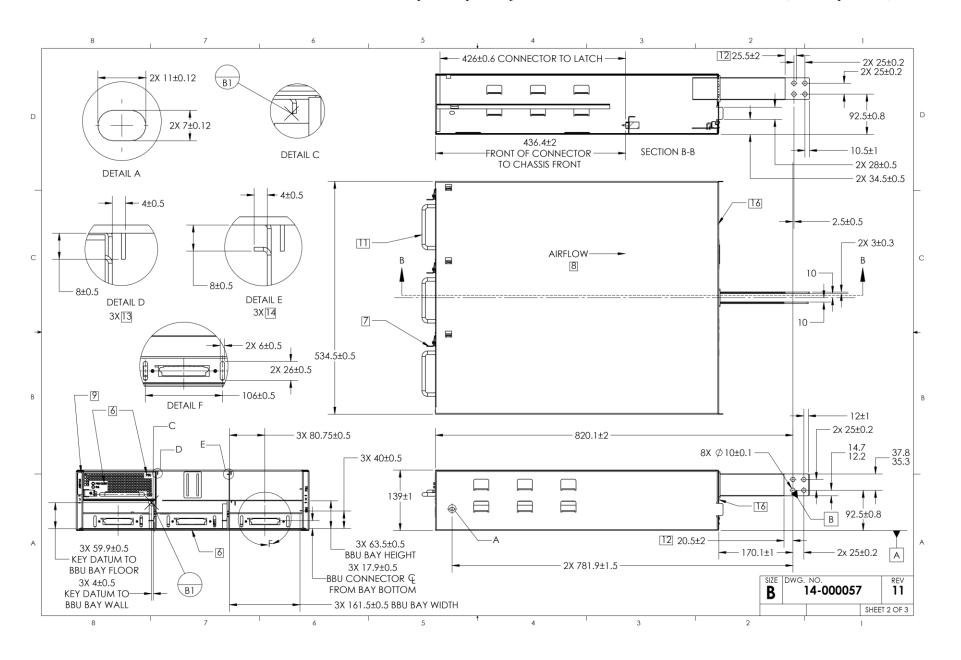

| 20 | Me   | echanic | al Dimensions                                | 48 |

|    | 20.1 | Pow     | er Module Dimensions                         | 48 |

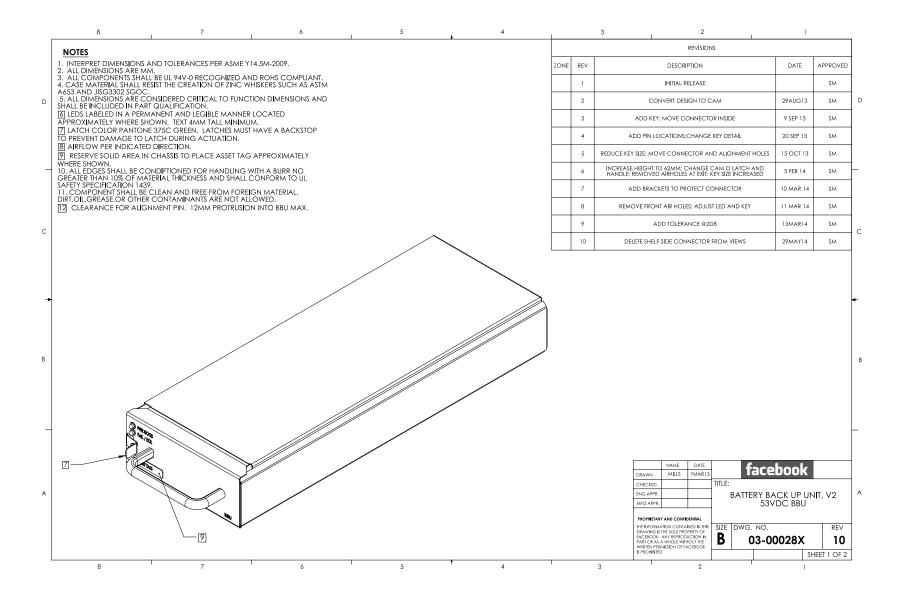

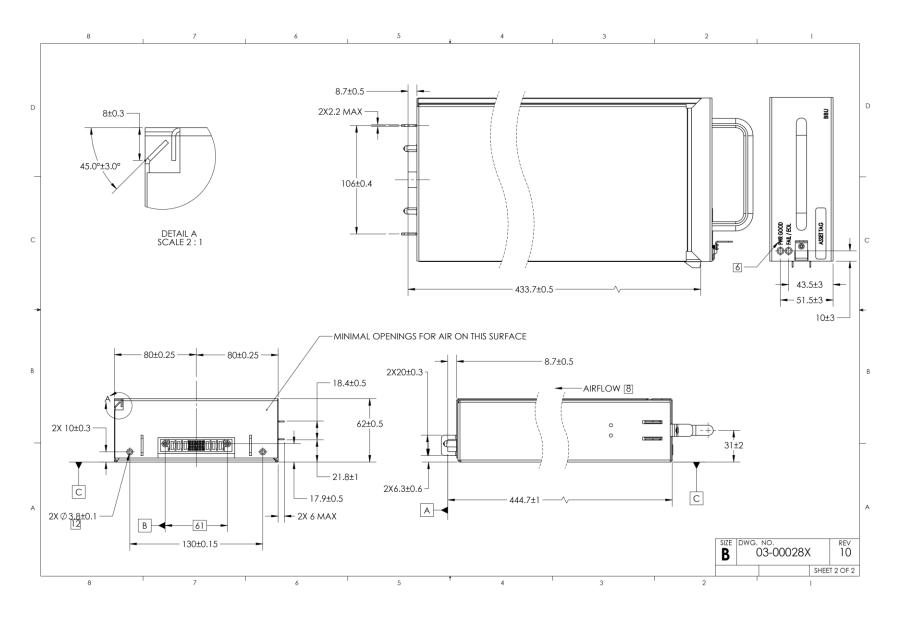

|    | 20.2 | BBU     | Dimensions                                   | 48 |

|    | 20.3 | Bus     | bar plating                                  | 48 |

|    | 20.4 | Shel    | f/Safety Labels                              | 49 |

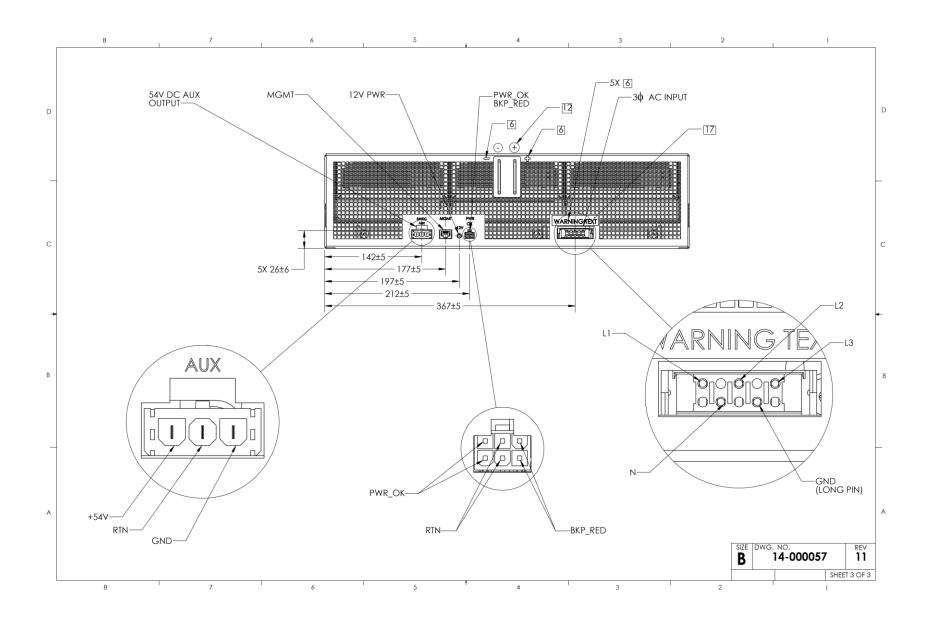

| 21 | Inp  | out and | Output Connectors                            | 49 |

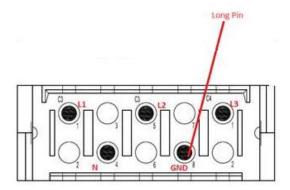

|    | 21.1 | AC l    | input                                        | 49 |

|    | 21.  | .1.1    | AC Surge Protection Inductors                | 50 |

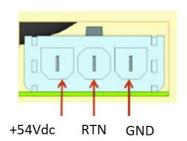

|    | 21.2 | Outp    | outs                                         | 50 |

|    | 21.  | .2.1    | 54Vdc Auxiliary Output                       | 50 |

|    | 21.  | .2.2    | Mgmt - RJ45                                  | 51 |

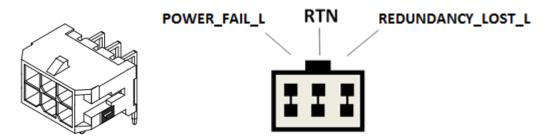

|    | 21.  | .2.3    | POWER_FAIL_L/REDUNDANCY_LOST_L               | 51 |

|    | 21.  | .2.4    | 12Vdc Output                                 | 51 |

|    | 21.  | .2.5    | 12Vdc Green LED                              | 52 |

|    | 21.3 | Inter   | nal Shelf Mating                             | 52 |

|    | 21.  | .3.1    | Output from the PSU                          | 52 |

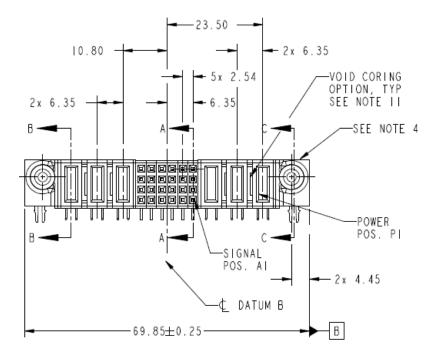

|    | 21.  | .3.2    | AC and DC Input for the PSU                  | 53 |

|    | 21.  | .3.3    | BBU Output                                   | 53 |

|    | 21.4 | Late    | hes/Other Connectors                         | 54 |

| 22 | En   | vironm  | ental Requirements                           | 54 |

| 23 | Me   | echanic | al Drawings                                  | 55 |

|    | 23.1 | How     | the PSU shall interrupt signals from the BBU | 60 |

|    | 23.  | .1.1    | Charge_Enable                                | 60 |

|    | 23.  | .1.2    | State of Health                              | 60 |

|    | 23.  | .1.3    | Stop_Discharge                               | 61 |

|    | 23   | 1.4     | Sleen                                        | 61 |

|    | 23.1.5     | End of Life                      | 61 |

|----|------------|----------------------------------|----|

|    | 23.1.6     | Fail                             | 61 |

|    | 23.1.7     | Protection                       | 61 |

|    | 23.1.8     | Insert                           | 61 |

| 2  | 3.2 Prote  | ection Levels for start up       | 62 |

| 24 | Introducti | on                               | 64 |

| 25 | Data Link  | Layer                            | 64 |

| 2  | 5.1 Stan   | dard and protocol                | 64 |

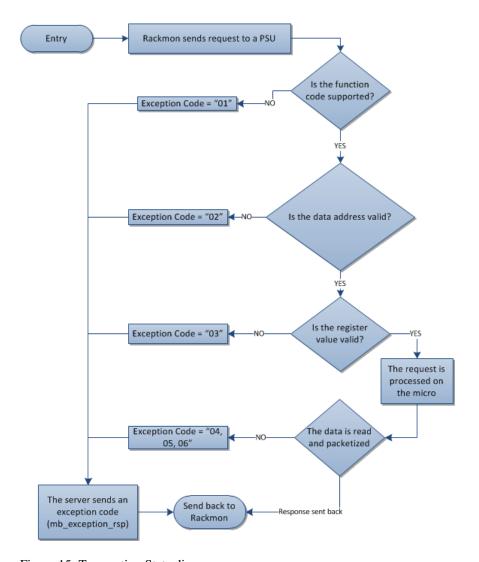

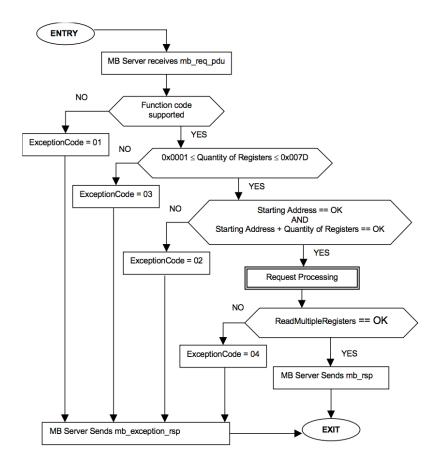

|    | 25.1.1     | MODBUS Transaction state diagram | 65 |

| 26 | Hardware   | Interface                        | 66 |

| 2  | 6.1 Add    | ressing                          | 66 |

|    | 26.1.1     | Message Frame                    | 68 |

|    | 26.1.2     | MODBUS Functions                 | 69 |

|    | 26.1.3     | Read Holding Register            | 70 |

|    | 26.1.4     | Register Mapping                 | 71 |

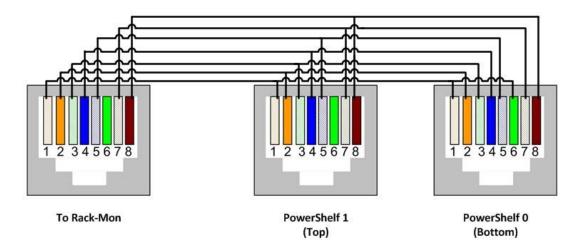

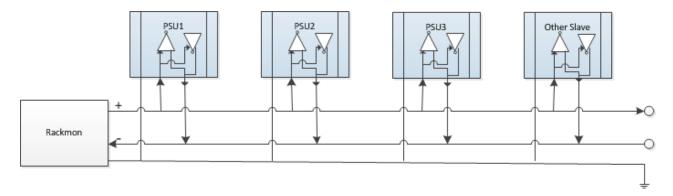

|    | 26.1.5     | Two Wire MODBUS implementation   | 71 |

|    | 26.1.6     | Register memory map for Slaves   | 75 |

#### 1 Overview

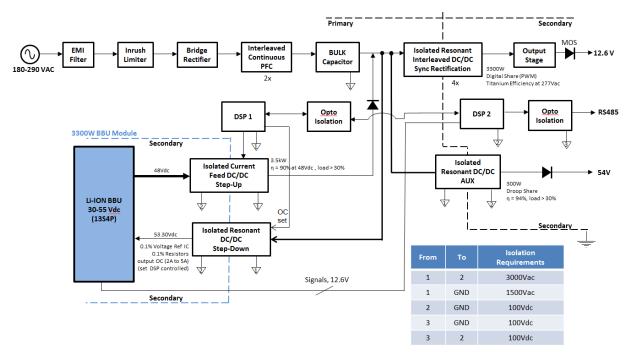

This document lists the requirements for the 6600W V2 Power Shelf (2 + 1) redundant, and the 3300W V2 Power Module. The V2 Power Shelf is three open units (OU) high. It hosts three power modules with the outputs connected in parallel. Each module is an AC/DC power converter rated at 3300W @ 12.6Vdc of nominal output power. It is hot swappable, has accurate current sharing and is self-cooled.

**NOTE**: 1 OU = 48 mm.

Each power module has its own BBU that powers the bulk voltage during an AC outage. In addition to the main 3300W DC/DC step-down converter, the power module also contains:

- A 3600W DC/DC step-up converter which is on during backup and supplies power to the bulk voltage via the BBU,

- A 270W DC/DC 52.5Vdc step-down converter for charging the BBU,

- A 300W DC/DC 54Vdc output auxiliary converter to supply power to the IT switches.

This V2 Power Shelf is fully compatible with OCP Open Rack V2. Throughout this specification, the V2 Power Shelf is referred to as Power Shelf, the power module as module, and the populated shelf (power station) as station (3 modules installed).

Please refer to the V2 BBU Spec document for detailed information on the BBU.

#### 2 License

As of January 5, 2015, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0:

Facebook, Inc.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at http://opencompute.org/licensing/, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT,

TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

## 3 Compliance Requirements

The power supply shall comply with the following standards as a stand-alone unit. It must be certified and labeled accordingly.

- 3.1 Safety Certifications, Applicable Documents

- UL60950-1 (Standard for Safety of IT Equipment)

- CAN/CSA-C22.2 No. 60950-1-03 (Standard for Safety of IT Equipment)

- EN60950-1:2006 / IEC60950-1 (Standard for Safety of IT Equipment)

- cCSAus Certification is allowed in place of the equivalent UL certification

- CE Mark, CB Report & Certificate

- EU Low Voltage Directive, EMC Directive

- UL94V-0 material flammability rating, with an Oxygen index of at least 28%

## 3.2 Immunity Standards, EMC

- EN61000 / IEC61000 applicable standards for Emissions & Immunity Requirements

- o EN61000-3-2 (AC Mains Harmonic Current Emissions)

- o EN61000-3-3 (Voltage Flicker)

- o EN61000-4-2, Level 4 (ESD)

- o EN61000-4-3 (Radiated Immunity, 3V/m)

- EN61000-4-4, Level 4 (EFT/Burst)

- o EN61000-4-5 (AC Mains Surge Immunity, see levels at § 5.9)

- o EN61000-4-6 (Conducted Radio Frequency Immunity, 3V/m)

- o EN61000-4-8 (Power Frequency Magnetic Fields)

- o EN61000-4-9 (Pulse Magnetic Field)

- o EN61000-4-11 (AC Mains Voltage Dips and Sags, Fluctuations)

- The power supply shall always resume operations after any fatal power line disturbance (PLD).

- Output voltage must never dip if backup voltage is applied to the PSU.

- Backup functionality is not affected by substantial repetitive dips and sags

- o GR-1089-CORE, Issue 4 PLD

- o BS EN 55024:1998, CISPR 24:1997 Information Technology Equipment

Note: When the power supply unit (PSU) is installed at the system level, the equipment under test powered by the PSU shall continue to operate without interruptions and/or resets during the above tests under EN61000-4-(\*).

## 3.3 Industrial Immunity Standards

• EN61000 standards for Industrial Immunity

- o EN61000-6-1 (Immunity / Light Industry)

- o EN61000-6-2 (Immunity / Industry)

This section of BS EN61000 applies to electrical and electronic apparatus intended for use in industrial environments. This standard applies to an apparatus that people intend to connect to a power network supplied from a high or medium voltage transformer that is

- Dedicated to the supply of an installation feeding industrial plants,

- Intended to operate in (or in proximity to) industrial locations.

This standard also applies to any apparatus that is battery operated and that people intend to use in industrial locations. The environments encompassed by this standard are industrial (both indoor and outdoor) and include locations where heavy inductive or capacitive loads are frequently switched, and have/or are in the presence of high currents and associated magnetic fields.

## 3.4 EMI Compliance & Limits

The AC main tests are conducted as a stand-alone unit, at 200Vac and 277Vac, and at full load (3300W + 300W + 270W):

- FCC Part 15, EN55022, CISPR 22: Conducted Emission, Class B (peak-reading)

- FCC Part 15, EN55022, CISPR 22: Radiated Emission, Class B

- The DC back-up converter shall meet Class A limits (no dB margin) with at 35Vdc input and full load

System Level: the power supply shall comply with Class A limits for both conducted and radiated emissions, with at least a 3 dB margin for both AC & DC inputs / converters.

- 3.5 Environmental Engineering Standards

- ETS 300 019-2-3, Class 3.2 (Operation)

- ETS 300 019-2-2, Class 2.3 (Transportation)

- ETS 300 019-2-1, Class 1.2 (Storage)

#### 3.6 AC Mains Leakage Current

The leakage current per module shall be in compliance with applicable EN/IEC standards, and shall not exceed 7mA RMS at 60 Hz and 277Vac.

## 3.7 Restriction of Hazardous Substances (RoHS) Compliance

The power supply is RoHS-6 compliant (BOM & Manufacturing Process)

- 4 AC Input Requirements (Main AC to DC converter)

- 4.1 AC Input Voltage, AC Loss Detection Time

- The AC input voltage range is 180Vac to 305Vac RMS (auto ranging).

- The nominal AC input voltage is 277Vac RMS (200-277Vac).

- The power module shall comply with the specification up to 290Vac RMS correspondent to 277Vac (+5%).

- All the components used in the AC input section shall have a voltage rating compatible with 300Vac operations, up to 305Vac (277Vac + 10%). The power module must withstand continuous exposure to 305Vac RMS input with no damage, while at this voltage level is not expected to meet the power factor and total harmonic distortion (THD) requirements.

- Input voltages higher than 310Vac RMS may damage the PSU.

- The front-end circuitry must be able to detect any AC loss within 5ms after the actual occurrence, at any

AC input level and at any phase of the input AC sinusoidal waveform (from 1° to 360°, wherever the AC

loss event occurs).

## 4.2 Input AC/DC PSU Connector, Fuse, EMI Filter

Each power module must have an AC input fuse. The fuse is used for safety and extreme protection in case of catastrophic failures. The AC input connector is polarized. The fuse is connected in series to the hot conductor (line). The fuse rating is a 25A. It is a slow-blow type fuse. It must never blow during inrush or during any AC input current transients. The fuse shall be a safety-approved component with rating of at least 400Vac RMS (it may be a larger size due to the high AC voltage involved). At the system level, the PSU is powered by a custom AC PDU connected directly to the tap box without any extra protection. a proper I2T coordination shall be verified when the PSU is powered by the PDU (e.g. in the event that the AC input stage of the power supply fails – a short circuit, for example – then the power supply input AC fuse should blow while the breaker in the tap box should not trip).

- The EMI filter should not make use of more than two cells with low series DC resistance. The design should preferably use bulky choke components in order to reduce the copper losses and maximize efficiency. Smart design of common mode (CM) windings that are able to include some differential (DM) impedance (DM leakage) is welcomed because it helps electromagnetic interference (EMI) suppression. As already mentioned, all the components used in the AC input power section must be rated at least 305Vac root mean square (RMS) (e.g. AC input connector, protection fuse, X2 EMI caps, surge protection devices, bleeder resistors, etc.).

- 4.3 Primary Metal-oxide Semiconductor (MOS) and BULK Caps

- The bulk capacitor shall be rated at 500Vac 105°C and shall have long-life components. For each bulk capacitor, a single component rated at 500Vac is required (compared to the potential alternative of having two capacitors rated at 250Vac each and connected in series). Voltage stress, especially when the positive peak of the low frequency ripple voltage at the worst conditions is included, is not negligible, while at the same time a reliable design, fully working up to 290Vac RMS input, must be guaranteed (305Vac RMS peak). See Section 5.5 for more information.

- The 500Vac rating gives enough margin for a nominal bulk voltage that shall likely be in the 430Vdc ~

440Vdc range.

All of the high voltage power metal—oxide—semiconductor field-effect transistor (MOSFET)s used in the primary side must be rated 600Vac (minimum), 650Vac is preferred.

NOTE: If a bridgeless type power factor correction (PFC) is chosen, it must have at least two high voltage silicon diodes (in series) from the AC grid. This is for safety. If the bulk voltage is energized by the Li-ion BBU during an AC outage, the bulk voltage (supplied by the BBU) must not be able to discharge to the AC input line after a single failure (e.g. in the event where one of the two diodes fail and create a short circuit).

## 4.4 AC Inrush Current, Preferred Topology

The inrush current shall never exceed 30A peak at cold start,  $V_{in} = 290 \text{Vac}$  RMS,  $T_{amb} = +35^{\circ}\text{C}$ . Perform the inrush test by synchronizing the positive (or negative) peak (90°) of the sinusoidal AC input voltage using a very low impedance AC source. Perform repetitive inrush sequences to validate the test. Make sure they are set at least one minute apart. The spikes of current due to the charging of the X2 EMI capacitors should not be considered. In realistic operations, the inrush sequence will have to repeat after any AC interruptions of sufficient duration to cause the PSU to enter back-up status, including dips and sags (i.e. multiple input dropouts). The PFC start-up current peak shall be lower compared to the AC inrush current peak. The AC inrush current during the main 12.6Vdc soft start up shall be less than 16A RMS at 230Vac. The inrush MOSFET or relay will be driven by the microprocessor. The inrush-limiting component (power resistor or NTC) will be placed in series to the input AC power train, before the input bridge rectifier (this topology will provide the best performance vs. the surge test). The relay must open and the sequence should be repeated every time the bulk voltage (BULK\_OK) falls below the bulk-low threshold.

## 4.5 AC Hold-up Time

The hold-up time is defined for the power module standalone without the DC input applied from the BBU. The minimum hold-up time shall be 20ms at full load (3300W main load + 300W auxiliary). A longer hold-up time may be required to reduce the peak start-up current from the BBU during back-up mode, if too high. Hold-up time is measured at full load, with no extra capacitance added to the output at  $T = 25^{\circ}$ C, sinusoidal 200Vac RMS, 50Hz, from when AC is lost at the  $0^{\circ}$  or the worst-case angle crossing, to when the output voltage falls below 12.0Vdc.

## 4.5.1 AC Drop Test

The power supply, including the auxiliary, shall remain in regulation when the AC input voltage drops to zero volts for half of a cycle at 50Hz, happening exactly at a 0° or the worst-case angle crossing, 200Vac, under a full load (3300W main converter + 300W auxiliary). Here are a few reasons why an extended hold-up time (and a reasonable size of the bulk capacitor) is needed:

- It can indirectly reduce the peak start-up current of the DC backup converter.

- It guarantees smooth back-up operations under all conditions (as mentioned above).

- It reduces the peak-peak low frequency ripple to limit the voltage stress on the bulk capacitors (they are used in PFC scheme working at up to 290Vac continuous).

• The target of this PSU is to obtain a very high efficiency during normal operation, so the nominal duty cycle of the DC-DC converter used after the AC-DC PFC state should be the highest possible – this implies the usage of bigger bulk capacitors for the same hold-up time.

# 4.6 AC Input Under Voltage Protection

The PSU shuts down during input AC under voltage and is able to automatically restart when a minimum voltage level is reached. The PSU shall turn on when the AC input voltage range is between 175 to 180Vac. The PSU shall turn off at 10 to 12.5V below the turn on voltage. No hiccups or on/off oscillations are allowed under any conditions.

The PSU shall withstand, without being damaged, multiple input dropouts under all conditions, and:

- It shall resume normal operations when no back-up voltage is connected to the PSU.

- It shall resume normal operations after multiple successful back-up sequences, when back-up voltage is connected to the PSU, without any output voltage dips.

- Input over voltage protection is not required.

## 4.7 Internal Bias Supply

The internal DC bias supply (auxiliary supply) is only intended for housekeeping functions (no externally available standby voltage is required). The implementation of an independent bias supply is the preferred solution and it should work from a minimum of 100Vac RMS (correspondent to 140Vdc on the bulk capacitors). The bias supply should be implemented with a high-efficiency scheme; the vendor shall propose the best solution.

A back bias connection that takes the 12.6Vdc from the common output busbar in the shelf, which is powered by the other PSUs, is needed. In the event of a PSU failure, the back bias will provide power to the failed PSU's secondary logic, communication circuits, and LEDs. The 12.6Vdc back bias shall not power any PSUs under normal condition (only when the PSU has a failure and cannot produce its own 12.6Vdc). Also, a thermal fuse – positive thermal coefficient (PTC) – and negative thermal coefficient (NTC) should be used as an internal short-circuit protection in conjunction with a resistor to limit the inrush current.

An analog circuitry shall be added to bring the REDUNDANCY\_LOST\_L signal low in parallel with the communication circuit in order to guarantee that we always know if a PSU has failed. We would like to compare the voltage before the Or-ing MOSFET transistor and compare it to around an 11V threshold. If the voltage reaches this threshold then it should be also used to drive the REDUNDANCY\_LOST\_L signal as well. Please use a comparator, half a volt of hysteresis to clear the signal, and around a one- second persistence delay. The voltage comparison threshold should set to 11V.

#### 4.8 Power Factor & THD

The PSU shall comply with EN61000-3-2 (see Section 4.2) up to 290Vac RMS input. See further requirements in Section 6.9.3.

## 4.9 Input AC Surge

See Section 4.2 (EN61000-4-5) with the following limits:

- 2kV DM (Differential Mode is line to neutral)

- 4kV CM (Common Mode is line/neutral to ground)

The power supply must be protected against surge events. It must not be damaged if a surge occurs. The PSU shall continue to operate without functional failures or hiccups during surge tests, per the above limits. Surge pulses should not affect the output voltage under any conditions. Surge events shall not be able to reset the system when the PSU is used in the final application at system level. At the system level, the PSU is powered by a custom AC PDU, which is directly connected to the tap box without any other protection or surge circuitry. Under these conditions, the PSU is expected to pass 2kV DM and 4kV CM (to be tested and verified), stand alone and at shelf level with (one, two or three) power modules installed in the shelf.

## 4.9.1 Primary Protection

The primary section (PFC, DC-DC) shall include an over-power protection rating higher than the PSU power rating. A small not-replaceable fuse may (or may not) be added in series to the bulk voltage feeding the following DC-DC converter. The vendor is free to define the best topology for safe operations.

## 4.9.2 Isolation Requirements

- The PSU will support safety-reinforced isolation between the high voltage AC primary section and any secondary section (3000Vac RMS of isolation).

- Isolation between the high voltage AC primary section and the chassis GND is 1500Vac RMS.

- Both positive and negative 12.6Vdc output terminations are floating with respect to the chassis GND, with a galvanic isolation of 100Vdc.

- The step-down, step-up, and auxiliary converters should also have the same reinforced isolation between the primary and secondary side (3000Vac). As a reminder, the negative returns of the auxiliary output and the 270W charger are electrically connected to the 12.6Vdc negative return.

## 4.9.3 High Potential and Ground Continuity

- The PSU shall be tested 100% in production for both high potential (with the applicable limits for the AC leakage current) and ground continuity (per the applicable standard). Stamps shall be applied to the chassis proving that both tests passed in production.

- The vendor must verify the ground bond test at the design stage, and it must comply with applicable IEC standards.

## Tech tips:

• A ground continuity test must be performed on the GND pin of a line cord-terminated product (normally the center pin of an IEC320 socket). This test verifies that the safety ground is present in the system. However, it does not test the ability of the safety ground to withstand a faulty current.

• Perform the ground bond test in a similar fashion to verify that a product's safety ground can adequately handle any fault currents due to insulation failure. The test duration may vary (it last up to 120 seconds).

## 5 DC Output Requirements (Main Converter)

## 5.1 Output Voltage and Power

The PSU is a single voltage power converter:

- The nominal output voltage is set to 12.6Vdc at 10% loading. See <u>Section 12</u> for the output voltage set point under share functionality (calibration will happen on the production line, during the final test). The surface mount technology (SMT) dividing resistors for output voltage reading shall be rated 0.1%.

- The output voltage regulation is ± 1% under any conditions. (input voltage, load, temperature, aging, etc.)

- The PSU shall withstand a no-load condition for an indefinite time, without damage and with (or without) the max allowed capacitive load connected to the output terminals.

- The nominal continuous output power is 3300W on the 12.6Vdc output.

- An output ORing metal-oxide semiconductor (MOS) is installed inside the PSU for current share, parallel

operations, and hot-swap conditions.

## 5.2 Output Over Current Protection

- The over current threshold is set to 280A (+5%, -2%) for the 12.6Vdc output. The protection mode during a short circuit or an overload is constant current mode. Output voltage must recover automatically when the over-current condition (or short circuit) is less than two seconds. The PSU is sized (thermally and electrically) to indefinitely stand a short circuit, without damage, under any conditions.

- An over-current condition lasting more than two seconds (± 0.2s) latches off the 12.6Vdc output only and

an AC recycle (≥ 1 second) is needed to resume operations. The two-second timer resets every time the

PSU exits the over current condition even for a very short time (>20ms typical).

- The PSU is able to start under overload or short circuit conditions.

## 5.3 Output Over Voltage Protection

- The over voltage threshold is set to 15Vdc.

- The protection mode is the latch off type, so an AC input recycle (≥ 1 seconds) is needed when attempting to resume operations after an over-voltage event.

- The over-voltage circuitry is independent, it includes a separate voltage reference device, and it does not

make use of the microprocessor to implement the function. The microprocessor may be notified in case of

an over-voltage event, if necessary.

## 5.4 Over Temperature Protection (OTP)

The PSU is protected against overheating to prevent damage or degradation. The PSU may overheat for many reasons, including (but not only) internal failing conditions, environmental factors, or because of improper use, such

as air obstruction. All the PSUs' outputs shut down for over temperature protection (OTP) and will not be able to automatically (needs an AC recycle) resume operations once the temperature falls below 10°C of the OTP limit (with some hysteresis). The OTP limit should be set as high as possible to maintain safe operation. No components shall be over stressed at the temperature shutdown threshold level. There should be enough temperature sensors within the PSU to guarantee safe operation. An OTP alarm for one PSU shall not force any of the other two PSUs in the shelf to also turn off. Each PSU shall act independently for OTP.

## For example:

- Primary thermal switch (e.g., normally closed for primary heat sink OT protection).

- Secondary thermal switch (e.g., normally closed for secondary heat sink OT protection).

- The BBU step-up, step-down BBU charger, and the auxiliary 54Vdc DC-DC converters should stay within their temperature range

- All of the thermal sensors should be routed to the microprocessor (primary sensors are opto- isolated). The vendor is free to propose the best solution for OTP.

The air inlet temperature sensor is needed to implement the fan's automatic speed control. An extra outlet temperature sensor is also added. The microprocessor oversees all PSU functionalities.

## 5.5 Capacitive Load

The maximum capacitive load at system level is  $200,000\mu F$ . A single PSU is able to start up properly and, more importantly, is unconditionally stable when such a capacitance (or a lesser capacitance) is connected to the output (in parallel to any resistive loads, or just the capacitance).

#### 5.6 Transient Response

The amplitude of the positive and negative output voltage peaks during a transient-load test shall be within  $\pm 2.5\%$  of the nominal output voltage ( $\pm 300$ mV), with a response time of <5ms, under the following conditions:

- Electronic load set in constant current mode.

- Current step-cycles from 50% to 100% of the PSU max load, at 50Hz dynamic load frequency, 50% duty cycle, and 1A/μs slew rate (min).

- Transient requirements shall be met with (or without) the max-allowed capacitive load connected to the output terminations.

## 5.7 Output Voltage Ripple and Noise

The max ripple and noise shall never exceed 200mV peak to peak of the 12.6Vdc output at 20Mhz bandwidth.

No external capacitive load is connected to the output terminals during this test. Measurements are performed at the output connector at PCB level, with the board installed in the chassis, a safety ground connected through an AC power cord, 180Vac input and full load. A digital oscilloscope is used for this measurement, with acquisition set to

peak detect mode. The probe will be used without its cap to minimize the length of the return connection in order to achieve a reliable R&N reading (negative return is directly connected to the metal body of the probe). A small 1uF X7R 0805 SMT ceramic capacitor may be connected locally to the probe tip during this measurement. As a design note, the 12.6Vdc output stage may include a small CM choke added very near the output connector, for CM noise suppression.

#### 5.8 Output Turn-on/Turn-off

Under any conditions of dissipative load, capacitive load, temperature, with backup voltage connected to the PSU, or without:

- The PSU shall turn on when a valid AC input is provided. Stand-by switch and/or on/off signal are not required. The design of the PFC & DC-DC circuitry, soft starts, etc., will be such that the total time, from when a valid AC input is applied to when the DC output voltage reaches regulation, is a maximum of two seconds under any conditions with Vin > 200Vac RMS.

- The 12.6Vdc rise time should be less than 20ms from 10% to 90% of the 12.6V output at any loading.

- The PSU is able to start properly during no-load conditions or overload conditions.

- For any loads (from no-load to max-load), the output voltage will rise monotonically from 0Vdc to 12.6Vdc, without overshoot or ringing, at any turn on following the application of AC input voltage, and anytime when the PSU resumes functionalities after an automatic protection condition (including parallel operations). The output voltage will fall monotonically from 12.6Vdc to 0Vdc, without undershoot or ringing, at any AC loss, and at any turn off caused by an automatic protection condition (including parallel operations). The backup voltage is not applied for this test, but the same performances are expected regardless of whether the input is supplied by AC or DC power (via the BBU).

- Output voltage shall never reverse polarity at the turn off (all conditions and converters).

- The PSU shall include a soft-start that promptly resets at any input AC loss of > 20ms, or after any automatic protection conditions.

- See <u>Section 7.1</u> for PSU behavior on AC loss, when a valid backup voltage is connected to the PSU.

## 5.8.1 Power Supply Turn-On Sequence

#### 5.8.1.1 Normal Conditions

After a valid AC input is applied, the internal bias supply turns on and the entire circuitry is powered. There is always a turn-on-sequence requirement when the AC input voltage is applied to the power supply, regardless of whether the DC backup BBU is installed. The three normal scenarios are described:

1. Every time AC is applied to the shelf including after the 90-second backup timeout: the shelf (3 PSU units) turns on synchronously.

- Sequence: After AC voltage is applied, the internal bias supply starts, the μP boots and keeps the PFC off as well as the step-up, step-down and auxiliary 54Vdc converter. Then the μP closes the inrush relay and turns on all of the converters. The step-down BBU charger is turned on two seconds after the main 12.6V is within regulation. (LED = solid green or solid yellow).

- 2. <u>AC restore during a backup lasting less than eight seconds:</u> the shelf turns on with a random delay between zero and two seconds.

- Sequence: After AC voltage restores, the μP keeps the PFC converter OFF. Then the μP generates a random number *n* between 0 and 2,000 turning ON the PFC with a delay equal to *n* milliseconds (LED = solid green). The shelf then sends a SYNC signal, which is dictated by the random number generated by the PSU module in slot #1. If the power module in slot #1 has failed (or is not even installed) at the time of AC restore during backup, the remaining two units start up at the end of Interval D (with no random time) synchronously, when AC becomes available and is present for at least one second.

- 3. AC restore during a backup lasting greater than eight seconds: the shelf turns ON with a random delay between zero and eight seconds.

- **Sequence**: After AC voltage restores, the μP keeps the PFC converter OFF. Then the μP generates a random number *n* between 0 and 2,000 and turns ON the PFC converter with a delay equal to *n*x4 milliseconds (LED = solid green). The shelf then sends a SYNC signal. The random number generated by the PSU module in SLOT #1 dictates the signal. If the power module in SLOT #1 has failed (or is not even installed) at the time of AC restore during backup, the remaining two units start up at the end of Interval D (with no random time) synchronously, when AC becomes available and is present for at least one second.

- The random numbers above shall be dynamically generated immediately after each AC recycle. They must not be generated one time and then stored in the EEPROM for future use.

- The PFC starts once the AC voltage is available, then the DC main 12.6Vdc converter and the 54V auxiliary

converters powered by the bulk voltage are turned on together (The vendor may add a small delay if needed)

followed by the step down charger to charge the BBU (if needed) after two seconds (maximum five-second

delay window).

- If the BBU in slot #1 fails before or during an outage so that the PSU in the master slot is not delivering 12V during back up, when AC power returns, the PSU in slot #1 shall still dictate the random timing and shall bring the shelf back synchronously out of back up. The PSU with the failed BBU during back up shall not turn on immediately when AC returns.

- o If the PSU in slot #1 is running an SoH test, and an AC power outage happens, then when AC power returns, the PSU in the other slots shall turn on synchronously without the random timing. [Same scenario as if the PSU in slot#1 has failed]

- If a BBU in slot #2 or slot #3 fails before or during an AC power outage, then when AC power returns the PSU in the master slot #1 shall still dictate the random timing and shall bring the shelf back synchronously out of back up. The PSU with the failed BBU during back up shall not turn on immediately when AC power returns.

## 5.8.1.2 Dead-Bus Event

As described above, when AC power gets restored during a backup phase after an AC power outage, the PSU will randomly restart in the two- or eight-second window. If the DC input (battery voltage) fails during that two- or eight-second window, in which the AC mains is actually available, or within the one-second filter window that is always present before the PFC starts delivering power (see Backup Sequence, interval D), then the PFC would provide power to the main converter instantly with reasonable output voltage (it shall not dip below 11.3Vdc during the Dead-Bus test at worst conditions and at full load). The backup sequence chart shows the exact point where to test the Dead-Bus event (see the complete backup sequence in the figures below). The PSU's 12.6Vdc output must stay within regulation and meet the DEAD-BUS requirement when battery voltage Vin(DC) ≥ 35 Vdc. The battery pack sends a stop\_discharge signal when the voltage level falls below 33.8Vdc (2.6V per cell), to protect the batteries from excessive discharge. If the back-up step-up converter in the power supply is still running when the battery voltage approaches the 33.8Vdc (2.6V per cell) cut off voltage, this means that an entire system shut down event is imminent (the standby emergency power generator did not turn ON, AC power is not available). Achievable Dead-Bus performance may be discussed during the design phase. Dead-Bus performances get worse at low temperature.

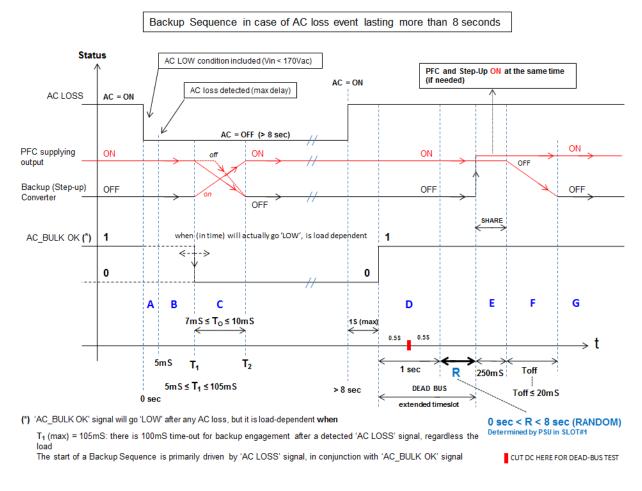

Figure 1: AC outage lasting less than 8 seconds transition sequence diagram

Figure 2: AC outage lasting more than 8 seconds transition sequence diagram

## 5.9 Microprocessor Control, Digital Bus, R&D Support

It is expected that all the logic and housekeeping function (over voltage excluded) are implemented and driven by a low-power-consumption microprocessor and low-power-consumption circuitry. This microprocessor oversees all PSU functionality. If a digital signal processor (DSP) is used to drive the pulse width modulations (PWMs), then it may (or may not) include the microprocessor functions.

The power module is entirely a digital power converter with the exception of an integrated circuit (IC) analog controller admitted only for the 300W auxiliary DC-DC (it provides 54Vdc output) and for the 270W DC-DC battery charger.

The three power modules are digitally interconnected with a separate internal digital bus (it does not go out from the shelf) for data exchange between the units, including: battery test priority, synchronized start-up and shut-down, randomization of the AC restart at shelf level, etc. If a PSUs internal (ex. CAN bus) communication fails and cannot receive message from any of the other PSUs then its fail LED should turn red, but it should still allow the main 12.6Vdc to provide power. The step-up, charger and auxiliary IT switch converter shall turn off.

**NOTE**: The shelf shall still be able to start up if all PSUs and BBUs are not installed.

The random restart command is assigned to the power module installed in SLOT #1: it enables the entire shelf to transition back to AC power for itself and to the two remaining modules, for a shelf synchronized random restart after the AC power restores (after outages). See Section 6.8.1 for more information.

A further independent RS-485 isolated digital bus is generated by each PSU, paralleled inside the shelf, and is connected to the RJ45 socket in the shelf's rear panel. This digital bus is used solely for data reporting. Such reports include power module failure, output/input power, and boot-loader function. It is possible to update the firmware of all the DSPs and/or microprocessors used inside the power module via the boot-loader through the shelf's RJ45 socket. Please refer to the V2 Communication specification for more information. The PSU shall blink green at 2Hz when the PSU is being updated via the boot-loader.

Input power reporting can be calculated accurately by measuring the output power and then dividing by the efficiency curve stored inside the EEPROM. There are two curves stored, at 5% load steps, from 10% load for the sole (PFC + main DC-DC) power converter:

- 230Vac

- 277Vac

The power module is able to determine when 230Vac range voltage or 277vac range voltage is applied to the PFC, and then select the proper efficiency curve to use for the back calculation of input AC power (in Watts).

The power module is able to shut-down the PFC by itself, to simulate an AC power outage for battery test purposes, every time the BBU that is connected to that power module requests a battery test. This periodic test is used as a status of health (SoH) check for the battery pack installed inside the BBU module. The BBU module also provides an end of life (EOL) signal when it needs to be replaced. When the battery test sequence is over (it can last minutes), the PFC resumes working using the AC voltage from the grid. It should not have any interruptions on the 12.6Vdc bus during the process. For the digital signals present during a battery test case, please refer to Section 7.2.4.

Several signals interconnect each power module with its own BBU, but not a digital bus. The PSUs can talk to each other via a digital bus, but the BBUs cannot. The BBU can only communicate via high/low signals to the PSU above it.

The firmware of the microprocessor and/or DSP must be upgradeable anytime during the life of the power supply. The design (and the vendor) must support the following:

• The PSU chassis cover shall have a small opening. The opening must provide access to a programming connector placed at the top of the logic board (it could be edge-pads on the PCB itself, or an equivalent location) that enables the user to upgrade the firmware easily without the need to uninstall the PSU cover. This opening is only required for EVT and DVT samples.

- A small indentation on the metal chassis or a mark will provide reference for 'pin 1' of the programming connector. The programming connector is only needed for EVT/DVT samples debugging (for PVT/MP the firmware can be upgraded by the shelf's boot loader).

- The vendor will supply the programmer needed to upload firmware, interconnection cables, functional software, and the set of instructions needed to upgrade the firmware at remote sites.

- The vendor will provide, free of charge, a reasonable amount of connectors, wire harnesses, and other items needed to qualify and use in their testing set up.

- The vendor will be able to provide quick new releases of the firmware code during development in order to speed-up fixes of any PSU issues, phase in improvements, system level bug fixes; including late findings or fine tuning.

- The vendor's R&D team is expected to be proactive and quick in resolving any hardware or firmware issues that may arise during the development, including potential technical malfunctions at the system level, or system integration issues.

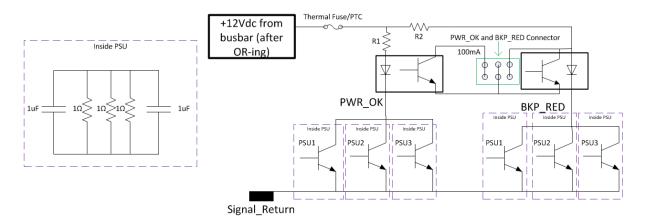

All signals return should be decoupled from the power return using three  $1\Omega$  high pulse current resistors in parallel (SMT1206) and 1uF capacitors on either side or the resistors between the negative return plane of the logic board and the negative return of the main 3300W DC/DC converter.

Figure 3: Signal ground decoupling schematic in the PSU

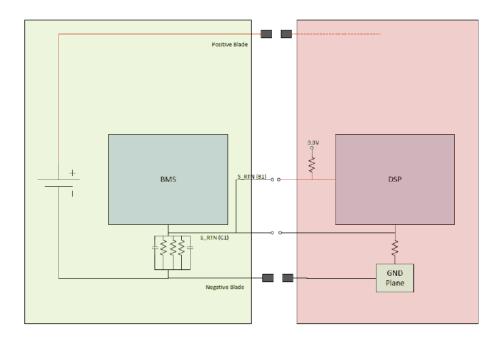

The figure below shows the signal ground decoupling in the BBU (left) connected to the DSP of the PSU (right)

Figure 4: Signal ground decoupling between BBU and PSU

Please refer to the V2 BBU, Battery Backup Module 3600W specification for the BBU signal and operation information.

## 5.9.1 Internal Cooling Fan, External Fan Guard

- The PSU must be self-cooled using either one or two internal power efficient fans pulling cold air inside the PSU (airflow is from front to back). The fan guard can either be built into the chassis sheet metal or into an external chrome plated fan guard. The PSU front is the side facing the cold aisle where the LEDs are installed. The fan mechanical mounting method should limit the propagation of vibrations to the PSU caused by the rotating fan. A soft rubber sheet material between the fan housing and the sheet metal chassis may be used for this purpose. The fan shall be installed using four flat head screws, properly located in order to avoid any potential air short circuits.

- The fan is a 12Vdc component. It's dimensions are 60mm × 60 × 25mm. the vendor can choose mm, min cubic feet per minute (CFM) (TBD), four-wire type, and double-ball-bearing type only. A reference fan is TBD.

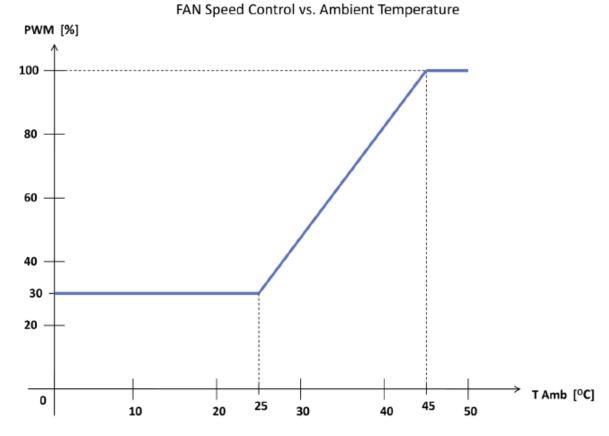

- The fan speed is driven by the microprocessor (the automatic speed control is based on the intake air temperature). The fan is used for PSU cooling purposes and for some extra airflow. The minimum duty cycle of the PWM signal applied to the fan shall be at least 30% (base value), no matter the PSU cooling conditions. Base speed is required because the PSU needs to provide some minimum degree of CFM air to the system. See the fan PWM [%] vs. Ambient Temperature graph below. The minimum fan speed (or PWM) should be not less than 30%. Higher than 30% PWM base value may be agreed upon, based on the actual thermal performances of the power supply.

- The air temperature sensor for the automatic speed control must be located near the air inlet panel. The fan shall not directly change speed with the output current level.

- The fan speed algorithm of the PSU should be computed while the PSUs are installed in the shelf and using the PSU that is inserted in the 'worst case' slot, which is the PSU with the highest back pressure (highest air flow impedance).

- At the PSU turns on, the fan should start up at full speed and then settle down to its self-regulated speed value.

- The fan is a 12Vdc component and so it can be powered directly by the output voltage. A C-L-C filter may be used to power the fan in order to reduce injection of spikes to the main 12.6Vdc supply output. In fact, the brushless fan generates significant amounts of ripple and noise to its DC supply. To endure the low frequency ripple current with extra margin (low ESR and long life component), the electrolytic capacitor connected directly in parallel to the fan must be selected.

- Layout Rule: At board level, the fan's positive and negative terminals are connected directly to the main output capacitors before any further PSU output filters, using independent dedicated copper traces routed away from any noise-sensitive circuitry (e.g. the main feedback loop circuitry, etc.).

- The microprocessor monitors the fan speed using the TACH signal and will shut down the PSU in the following cases:

- o Fan failure

- Fan blockage

- Inconsistent fan speed readings.

- Under any fan failure conditions, the FAIL (red) LED will turn on and the PSU will shut down (see <u>Section 18</u>).

- If two fans are used and one fan fails, the event should be treated as a fan failure and the PSU should turn off.

- The fan will always run at full speed during a back-up phase or battery test.

- The fan must stay on at full speed for at least 1 minute after a backup lasting more than 30 seconds or a battery test before going back to its normal self-regulated speed.

- The fan L10 life shall be at least 50 000 hours at a 45°C inlet air temperature and full speed (to be verified with the fan vendor)

Note: The battery back up can last up to five minutes at 2,200W constant power or the backup converter can provide constant power for 3,300W for up to 90 seconds. During battery back up the fan should run at full speed.

# 5.9.2 Power Supply Efficiency (AC Main Converter)

The PSU cost and actual measured efficiency (pilot samples) can be used for internal TCO evaluation and analysis.

Efficiency shall meet Titanium efficiency limits at 277Vac (the 52.5V battery charger and the 54Vdc AUX output converters are completely disabled [inputs are not connected during efficiency measurements]. All fans are powered externally and all voltages measurements at PCB).

The Titanium efficiency limits are as follows:

- 90% at 10% of the load

- 94% at 20% of the load

- 96% at 50% of the load

- 91% at 100% of the load

Further efficiency target requirement:

• Efficiency > 95% between 30% load to 90% load at 277Vac input

Measurements are performed as follows:

- Input AC power voltage of 277Vac RMS (50Hz or 60Hz)

- A power analyzer with reading accuracy better than 0.1% will be used for the measurements

- A precise low distortion AC power source supplies the input voltage during the measurement

- The PSU board is correctly installed in the chassis, with the cover and with the safety chassis GND connected through the AC power connector.

- AC- and DC-power input voltages are measured directly at the respective PCB pads.

- Fans should be powered externally.

- The output 12.6Vdc measurement shall be made at the output of the busbar blades of the PSU at PCB level.

- The ambient temperature should be around 25°C.

- The measurement load step shall be an increment of 5%. Take measurements after 30 minutes under initial 75% load, over five samples (they all need to pass).

NOTE: The PFC may include interleaved topology with phase management in order to maximize the efficiency at light load (phase shedding).

## 5.9.3 Power Quality

THE power factor and iTHD (total harmonic distortion of the AC input current, with order of the harmonics up to and including 40) at 200-300Vac shall be:

- PF > 0.95 (>10% of max load)

- iTHD < 10% (>10% of max load)

The vendor is encouraged to propose solutions exceeding the above limits if they make cost sense for a 3,300W power supply. Efficiency is the first priority.

Measurements are performed from the same test set up as described in <u>Section 6.9.2</u>.

## 5.9.4 Stability

- The power supply shall be unconditionally stable, under any conditions or combinations of resistive and capacitive loading, constant power loading, temperature, aging, etc. Feedback loop control (analog or digital) shall never cause the E/A to enter a non-linear status during extreme transients.

- The Bode plot will show a phase margin better than 45 degrees at worst conditions (or 60 degrees at nominal conditions), and the dynamic step-load plots (see Section 6.6) will show no ringing. Rather, they will show a smooth recovery shape similar to a second order system with a damping factor  $\sigma > 0.7$ .

- The stability criteria is met with and without the maximum allowed capacitive load.

- The stability margin should not be excessive. Exaggerated reductions of the line frequency ripple or slow transient response time are not desired.

## 6 Battery Backup Section (Back-up Converter)

The power supply is able to provide short term backup power in case of an AC power outage. To enable this function, an independent isolated DC-DC power converter capable of 3,600W+300W, and an independent isolated 270W step down DC-DC power converter will be included within the PSU to provide power during backup and charging of the Li-ion batteries. The target is to provide seamless backup performance and enable smooth operations under any conditions, such as transients of AC power input, so as to be equivalent at system level to an online UPS.

## 6.1 Summary for the Whole Back-up Section Requirements.

For the backup power converter, all the input and output requirements, performance, compliance requirements, etc., are equivalent to what was specified for the DC main converter, powered by the high voltage bulk. The output of the back-up converter will also power the high voltage bulk. Additionally, there is an auxiliary isolated 300W DC-DC power standalone converter, which is powered by the bulk voltage. It outputs 54Vdc to the IT switches.

## 6.2 Signal Definitions:

Below are some definitions of some shelf-level signals:

AC\_LOSS: This is an internal signal reporting the status of the AC power input voltage. This signal is required to change status within 5mS after an AC power loss event, which may occur at any phase angle of the input AC power sinusoidal waveform (50Hz or 60Hz, 180Vac to 290Vac RMS).

BULK\_OK: When the energy in the bulk capacitors of the power modules drops below a minimum threshold. This is an internal to the PSU signal reporting the status of health of the bulk voltage:

- AC BULK OK = good (logic status '1') if bulk voltage > 90% of its nominal value.

- AC BULK = no good (logic status '0') if bulk voltage < 85% of its nominal value.

- Hysteresis = 5%

POWER\_FAIL\_L: This is an active low open collector signal. It is normally high. This signal is sent low out of the shelf via pin 2 on the RJ45 connector every time the following condition occurs:

At 45 seconds into backup mode if AC\_OK is still not present (three phase AC outage), then send out the POWER\_FAIL\_L signal and then at 90 seconds shut down the power shelf for a timeout.

**NOTE**: The POWER\_FAIL\_L signal is not for a sudden failure, a sudden over current condition, or a lack of energy in the BBUs, which may cause the shelf to shut down. An SoH should not cause the POWER\_FAIL\_L to be asserted.

REDUNDANCY\_LOST\_L: This is an active low open collector signal. It is normally high. This signal is sent low out of the shelf via pin 3 on the RJ45 connector every time the following condition occurs:

- When the Power Shelf loses redundancy. This means that at least one power module in the shelf has failed (red LED on the PSU), a BBU in the shelf has failed, or the sleep/insert signal is high.

- The REDUNDANCY\_LOST\_L signal should also be asserted when the PSU is performing a bootload or when the BBU voltage is below 31.85Vdc.

**NOTE**: An AC power outage/backup or one BBU performing a battery test should not make the REDUNDANCY\_LOST\_L signal go low. The REDUNDANCY\_LOST\_L signal may go low if any of the above requirements are met while in AC power outage mode. For example, if a PSU fails during an AC power outage the REDUNDANCY\_LOST\_L signal should go low. The signal should also not assert when any BBUs in the shelf have the Stop\_Discharge/Protection signal low.

The POWER\_FAIL\_L and REDUNDANCY\_LOST\_L signals will also be used to drive a simple 9Vdc 1A regulator driven by the external 12Vdc common bus (via thermal fuse, etc., for protection) and activated by the logic present in the shelf. The 9Vdc shall turn on (be driven high) and be present on the Molex Minifit connector when the POWER\_FAIL\_L and REDUNDANCY\_LOST\_L signals are asserted low, (discussed in Section 22.2.3) at the back of the power shelf within 500µs.

SYNC: There should be a few SYNC signals reserved to be used for synchronized PSU turn-on and turn-off. The vendor can add other shelf-level signals.

## 6.2.1 Shelf AC Turn On Sequence

Initial AC power turns on, regardless how many PSU and BBU modules are inserted.

- 1. The PSU checks to make sure that all PSUs inserted in the shelf have AC\_OK as well as BULK\_OK signal asserted high. If any of the PSUs AC\_OK or BULK\_OK signals are low, the PSU will make the AC\_OK and BULK\_OK shelf level signal low.

- 2. Once both shelf-level signal of AC\_OK and BULK\_OK signal are good, a SYNC signal is given to turn on the PSUs synchronously.

- The 12.6V and 54Vaux turn on together, first (the vendor may add a delay if necessary), followed by the battery charger which will turn on with an initial two-second delay if the Charge\_Enable signal is low from the BBU.

## 6.2.2 Shelf AC Turn Off Sequence

- 1. If AC power input is removed from the shelf, the PSU will enter the backup sequence and wait for AC power to return within 90 seconds.

- a. If AC power does not return within 45 seconds the PSUs will assert the POWER\_FAIL\_L signal low and at 90 seconds should turn off the PSUs synchronously.

- 2. If there aren't any BBU units installed in the shelf, the shelf shall synchronously shutdown the 12.6Vdc output monotonically when the AC input is disconnected from the shelf.

Please see Section 7.2 for more information of when the shelf shall always shut down synchronously and assert the POWER\_FAIL\_L signal.

NOTE: If AC power returns anytime before the 88th second, the 90-second timer shall be ignored. This guarantees that the shelf does not turn off due to the eight-second random window.

## 6.2.3 Backup Sequence

- 1. As long as the BBU is inserted and has not failed/sleep (INSERT and BBU\_FAIL signals) the PSU module may power the bulk voltage from the Li-ion batteries via the step- up converter.

- The PSU should request power from the BBUs when both the AC\_LOSS signal is low (the AC input fell below the minimum threshold Vin < 170Vac RMS) and the AC BULK\_OK signal is low (bulk voltage fell below the minimum threshold). The power modules can independently go into backup.

- As per <u>Section 5.1</u>, any sinusoidal AC power loss must be detected within 5ms after the actual loss.

- Backup Engagement Timeout: There is a 100ms timeout for backup engagement after a continuous detected AC loss, regardless of the status of AC BULK\_OK. At high load the AC BULK\_OK signal changes status a few milliseconds after the AC\_LOSS does (it triggers the backup engagement). But the AC BULK\_OK status is load-dependent and so it may not trigger before 100ms, while the backup sequence would engage for the 100ms timeout. The transition from AC power mode to DC power mode will last a maximum of 10ms, in which the two converters, PFC and backup step-up, will gracefully exchange the load. During the transition from the bulk voltage being powered from the AC line or from the BBU, output voltage dips and spikes must stay within ±2% of the output voltage as it is set to as full load conditions. The vendor is required to control the transition between power coming from the PFC and DC power step-up converter during transitions in to and out of the backup sequence. For example, the step-up converter could be set at 400Vdc and then be slowly brought to nominal bulk voltage. This is particularly useful to limit the BBU startup current.

- In normal conditions when a valid AC voltage is present, the PFC delivers power to the bulk voltage and

the step-up converter is kept off to enhance the overall PSU efficiency. However, it is ready to kick in at

any AC power loss.

- 4. If during a backup phase the AC power comes back, the PFC will start powering the bulk voltage only after a continuous valid AC input voltage is present for at least one second. It will transition the load between the PFC and the step-up converter for 0.25 seconds. If AC\_LOSS or BULK\_OK signals toggle during the timing intervals above, the counters (one second or 0.25 seconds) will reset and start over. At the end of the 0.25-second portion, the DC backup step-up converter will phase out in <20ms, releasing the full load back to the PFC. The target is to generate a backup sequence mode that guarantees the highest rejection against input AC power disturbances/random dips. It also guarantees UPS-grade performance during AC power

outages. The vendor is encouraged to propose the best refined timings vs. the actual topology adopted for best performance.

- 5. The backup phase will last for no more than 90 seconds at full load (3,300W + 300W) at 33.8Vdc at 45°C.

- Backup Phase Time Out: the power supply will shut down after a continuous 90 seconds of backup operations. This functionality shall be built in the logic of the power supply.

- 6. The fan(s) will run at full speed during the backup phase.

- 7. If there is not enough energy in the BBUs installed in the Power Shelf to reach 90 seconds, then a POWER\_FAIL\_L asserts at 45 seconds.

- 8. Dead-Bus sequence: See <u>Section 6.8.1</u>.

**Design**: The target of the design is to provide a seamless output voltage level no matter what happens to the AC input voltage if a valid BBU voltage is applied to the power module. The discontinuity of the AC power can be a simple AC outage, or a sudden dip, glitch, disturbance, etc. The vendor is encouraged to propose the best solution that meets or exceeds the specified requirements without sacrificing cost and performance.

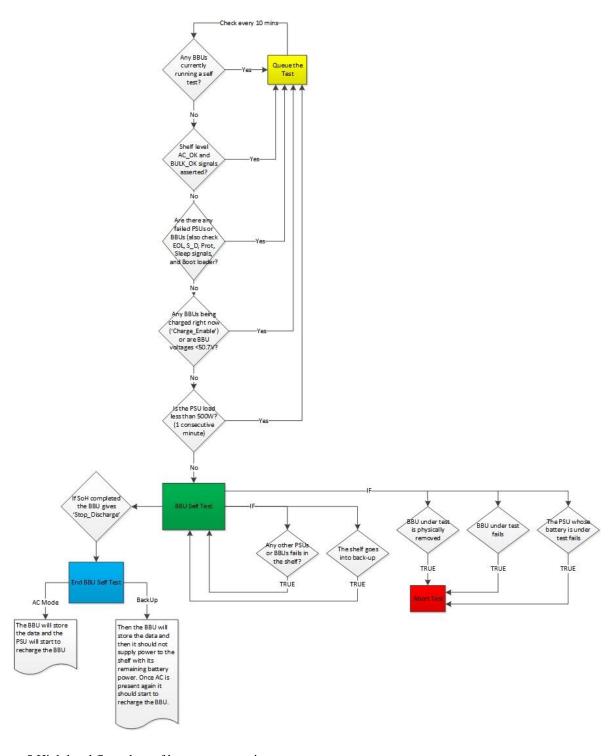

## 6.2.4 Battery Test Sequence

The BBU will determine internally (with random logic) when the BBU needs to be tested. Please refer to the V2 BBU Spec for more information. The logic of how a BBU test should be implemented once the SoH signal is low appears below.

The PSU will turn off the step-up converter and stop using the BBU as a source of power once the SoH signal is high. At any time during the battery test, when the SoH signal is low, if the BBU gives the 'stop\_discharge' or 'fail' signal the PSU shall stop using the BBU as a power source.

- 1) CHECK: Make sure all three PSUs and BBUs are installed and communication is available.

- 2) CHECK: Are any BBUs currently running a self test? This is determined via internal communication.

- YES: Queue the test

- No: Continue

- 3) CHECK: Are the shelf level AC\_OK and BULK\_OK signal valid (AC power is present to all three PSUs)?

- YES: Continue

- No: Queue the test

- 4) CHECK: Are there

- Any failed PSUs or BBUs

- Any BBUs displaying the following low signals:

- Stop\_Discharge

- o EoL

- Protection

- Any BBUs with a high Sleep or Inert signal,

- Any PSUs in the shelf performing a FW update (boot loader)

- YES: Queue the test

- No: Continue

- 5) CHECK: Are there any BBUs being charged at the moment via the Charge\_Enable signal or are there <u>any</u> BBU packs with a voltage less than 50.7Vdc?

- YES: Queue the test

- No: Continue

- 6) CHECK: Is the load greater than 500W for at least one minute (consecutively)?

- YES: Continue (if load decreases during the test, continue. Once you perform a test you must commit to it)

- No: Queue the test

- 7) START self test

- IF another BBU fails or another PSU in that shelf fails

- i. THEN continue the test as normal

- IF the shelf goes into backup mode

- i. THEN continue the test as normal

- IF the BBU is physically removed

- THEN end the test. The BBU will consider this as a failed test and wait for the next scheduled test.

- IF the PSU whose battery is being tested FAILS

- i. THEN ABORT test (BBU goes into sleep mode)

- 8) IF SoH re-asserts high, or if Fail or Stop Discharge appears, then the PSU will stop discharging the BBU.

- Determine if the test is valid:

- i. The BBU will determine the validity of the test data> If valid, it will begin its open circuit voltage (OCV) period and will determine if the BBU has reached EoL at the end of this period. During this period the BBU will not be recharged. The charge\_enable signal will remain high.

- IF for any reason during this OCV period the battery asks to be charged ('Charge\_enable' is low) this means that the test data was not useful and the BBU has aborted the test.

- 2. IF an AC power outage occurs during this OCV period, the outage is always given priority and the PSU can use the BBU as a power source, until the stop\_discharge signal is given. The BBU will abort its battery test.

- Once that BBU has been fully recharged, the PSU will consider the test complete and will allow another BBU to be tested if it was in queue.

- 9) During a battery test the internal digital BUS informs the other power modules installed in the shelf that they cannot perform any battery tests until:

- The current test completes

• The module performing the battery test recharges

If multiple BBUs are in queue at the same time, base the priority of the battery tests on the slot number (first Slot #1, then Slot #2, and finally Slot #3). For example, if the BBU in Slot #3 entered the queue, followed by the BBU in Slot #1, then the BBU in Slot#1 will perform its battery test first. If an SoH signal was low for a BBU prior to an AC outage (a PSU was in queue for any reason) then the PSU should go into battery backup. Once the outage is over, the PSU shall return to AC power. The BBU SoH signal will change from low to high, assuming a battery test was performed (the BBU will try to use the discharge data to figure out if the data is valid of not) and will ask to be checked again, via the SOH signal in 90 days.

Use the following flow chart as a high-level reference. Please follow the detailed checks mentioned above.

Figure 5:High level flow chart of battery test requirements

## 6.3 Charge Sequence

The step down charger will only turn on for two seconds after the charge\_enable signal from the BBU becomes low. The BBU's internal charge MOSFETs will close as soon as the charge\_enable signal becomes low. See Section 9.2 for more information regarding the output of the battery charger converter.

## 7 Battery Backup Unit

Please refer to the latest V2 BBU, Battery Backup Module 3,600W specification for this section. The V2 BBU specification will have details about the connector, signal and pins, logic, and operation of the BBU.

#### 7.1 12Vdc from the PSU to the BBU

The PSU shall power the LEDs on the BBU via its 12Vdc output. Four pins will be reserved on the PSU FCI connector, two pins for +12Vdc and two pins for return. The 12Vdc should be taken before the output 12Vdc ORing MOSFET inside the PSU. This is to ensure that if the PSU fails the BBU will go into 'sleep mode' since the 12.6Vdc will not be present (Section 8.1 in the V2 BBU Spec). Note, that the layout for this connection needs to be done in such a way that the electrical noise generated from the BBU does not pollute the 12.6Vdc output of the main power module. A thermal fuse should be placed on the positive output of this connection.

#### 7.2 BBU Latched Condition

For the BBU, a latched off signal indicates that one of the EoL or FAIL signals are asserted. Both signals are independently latched off. See Section 18. The method used to guarantee the latching-OFF condition of the EoL signal (and yellow LED) and of the FAIL signal (and red LED), may involve corresponding information being written by the BBU logic in the non-volatile memory EEPROM used in the BBU. Removing a BBU unit from the slot and re-installing it in the slot, with or without the presence of 12V at shelf level, cannot reset the latching-OFF condition.

## 7.3 BBU Signals

There are eight analog signals that the PSU will receive from the BBU:

- Fail

- Charge Enable

- SoH

- EoL

- Stop Discharge

- Sleep

- Protection

- Insert

All of these signals are normally high except the Sleep signal, which is normally low. When the Sleep signal is high, it indicates that the BBU has gone into a software sleep mode. The Insert pin is also normally low when inserted into

the shelf. The PSU shall implement a minimum of a one-second persistence delay before it takes the appropriate action. The PSU shall not try to use the BBU as an energy source if the Stop\_Discharge signal goes low. If the Stop\_Discharge signal is asserted low, the PSU shall ignore it for the first 15 seconds into the backup. If the signal is still low at 16 seconds, then the PSU shall stop discharging the BBU. After the initial 15 seconds of backup, the persistence delay of the Stop\_Discharge signal shall change to one second. If the Fail signal is low, the PSU shall not discharge or charge the BBU. If the Sleep signal is high, the PSU shall not try to use the BBU (both these signal shall also have the one-second delay). If the SoH signal is low and all requirements are met in Section 7.2.4, then the PSU shall discharge the BBU until the SoH signal becomes high. The PSU shall only charge the BBU when the Charge\_Enable signal goes low. In the odd case that the Charge\_Enable signal goes low during a BBU discharge, the PSU shall ignore it and shall not charge the BBU while the step-up converter in the PSU is delivering power.

## 7.4 BBU Leakage Current

The leakage current at 52.5Vdc main output blades (including the sense lines) from the BBU input should be a maximum of 2mA regardless of the what state the power supply is in (ex. on, off, failed, etc.).

## 8 Backup Converter – Step Down

## 8.1 DC Input Requirements

The input of the 270W step-down DC-DC battery charger converter will be connected directly to the bulk voltage of the main converter. This converter will provide  $52.5 \text{Vdc} \pm 0.2\%$  for battery charging purposes. It is a stand-alone analog converter, powered by the bulk voltage, reinforced, isolated, and hot pluggable. This converter connects directly to the Li-Ion BBU battery module with an ORing diode/MOSFET, to avoid the spikes of current that occur when a charged BBU is installed in the shelf (it blocks the voltage from the BBU). It is activated/deactivated by the DSP/microprocessor. The leakage of the ORing diode/MOSFET shall be less than 0.5 mA and two  $100 \text{k}\Omega$  in parallel before the ORing shall be placed in parallel to the output capacitors so that the output capacitors do not become charged to 52.5 Vdc and do not fake the converter into seeing a correct voltage if the step down converter does not work.

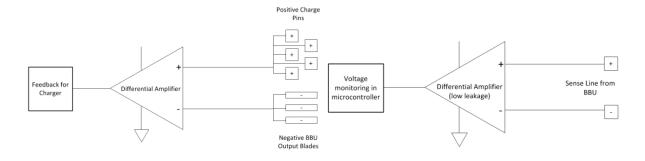

The feedback for the step down charger shall be taken at the three power blades of the negative connector of the battery and the five positive charge pins with a differential amplifier. The sense lines provided from the BBU will be also connected to a differential amplifier used for monitoring the battery voltage.

Figure 6: Block diagram of how differential amplifiers should be connected to the battery

## 8.2 DC Output Requirements