# Open Accelerator Infrastructure (OAI) OCP Accelerator Module (OAM) Base Specification r2.0 v0.75

**Author: OCP OAI Workstreams**

# **Table of Contents**

| 1 | Lic | ense   |                                                   | 5  |

|---|-----|--------|---------------------------------------------------|----|

| 2 | Coi | mplia  | nce with OCP Tenets                               | 6  |

|   | 2.1 | Оре    | enness                                            | 6  |

|   | 2.2 | Imp    | pact                                              | 6  |

|   | 2.3 | Sca    | le                                                | 6  |

|   | 2.4 | Sus    | tainability                                       | 6  |

| 3 | Acl | knowl  | ledgements                                        | 7  |

| 4 | Ov  | erviev | <i>N</i>                                          | 8  |

|   | 4.1 | Sco    | pe                                                | 9  |

|   | 4.2 | Acr    | onyms                                             | 9  |

| 5 | Hig | h-Lev  | vel Specification for the OCP Acceleration Module | 10 |

| 6 | OA  | M Me   | echanical Specifications                          | 11 |

|   | 6.1 | Мо     | dule PCBA Form Factor                             | 11 |

|   | 6.2 | Me     | zzanine Connector                                 | 14 |

|   | 6.2 | .1     | Mate/Unmate Force Data                            | 15 |

|   | 6.3 | OAI    | M Top Stiffener                                   | 17 |

|   | 6.4 | OAI    | M Bottom Stiffener                                | 17 |

|   | 6.4 | .1     | Tolerance Stack-up of Bottom Stiffener            | 19 |

|   | 6.4 | .2     | Alignment Pins                                    | 19 |

|   | 6.4 | .3     | EMI Gaskets / Pads                                | 21 |

|   | 6.4 | .4     | Die Springs                                       | 22 |

|   | 6.5 | Bas    | eboard Keep out Zone & Grounding Pads             | 24 |

|   | 6.5 | 5.1    | SMT Nut                                           | 24 |

|   | 6.5 | 5.2    | Component Keep-out Zone                           | 25 |

|   | 6.5 | 5.3    | Grounding Pads                                    | 25 |

|   | 6.6 | Rec    | commended Alignment Features                      | 25 |

|   | 6.7 | Ref    | erence Heatsink Design                            | 27 |

|   | 6.7 | '.1    | Top Handle                                        | 27 |

|   | 6.7 | '.2    | Long Screw Attachment                             | 28 |

| 7 | The | ermal  | Specification                                     | 29 |

|   | 7.1  | Environmental Conditions                                            | 29 |

|---|------|---------------------------------------------------------------------|----|

|   | 7.2  | Temperature Report                                                  | 30 |

|   | 7.2. | 1 Temperature Sensors                                               | 30 |

|   | 7.2. | 2 Remaining Components                                              | 30 |

|   | 7.3  | Thermal module information                                          | 30 |

|   | 7.4  | Heatsink Assembly                                                   | 30 |

|   | 7.5  | Thermal Recommendation                                              | 31 |

|   | 7.5. | 1 Airflow Budget                                                    | 31 |

|   | 7.5. | 2 Reference Heatsink Design                                         | 31 |

|   | 7.5. | 3 Thermal Interface Material                                        | 33 |

|   | 7.5. | 4 Heatsink Installation                                             | 34 |

|   | 7.6  | Liquid Cooling Requirements                                         | 35 |

|   | 7.6. | 1 Boundary Conditions                                               | 35 |

|   | 7.6. | 2 Reliability Expectations                                          | 35 |

|   | 7.6. | Reference Coldplate Design                                          | 35 |

|   | 7.6. | 4 More Recommendations                                              | 37 |

|   | 7.7  | Consideration for Immersion Cooling                                 | 37 |

| 8 | OAN  | Л Electrical Specification                                          | 38 |

|   | 8.1  | Electrical Connector                                                | 38 |

|   | 8.2  | OAM Connector Pinout Quadrants                                      | 39 |

|   | 8.3  | OAM Pinout Description                                              | 40 |

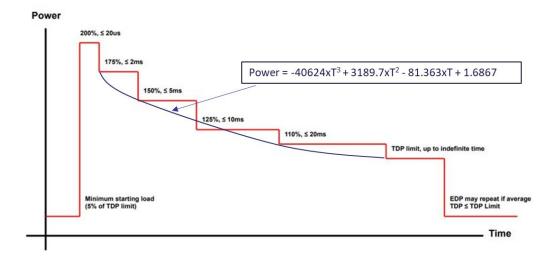

|   | 8.4  | OAM Power Profiles                                                  | 47 |

|   | 8.4. | 1 Thermal Design Power TDP                                          | 47 |

|   | 8.4. | 2 Excursion Design Power EDP                                        | 48 |

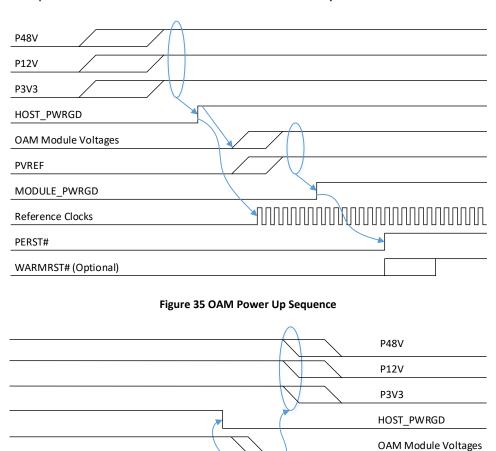

|   | 8.5  | System power sequencing                                             | 49 |

|   | 8.6  | OAM Insertion Loss                                                  | 51 |

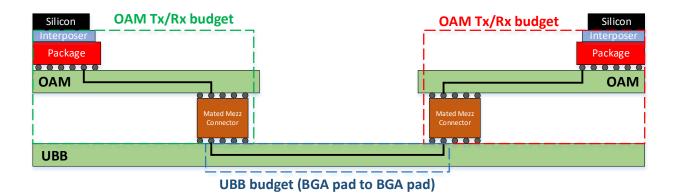

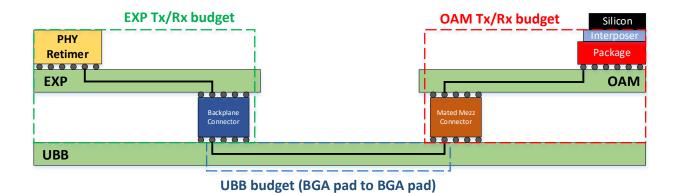

| 9 | OAN  | Л Interconnect Topologies                                           | 53 |

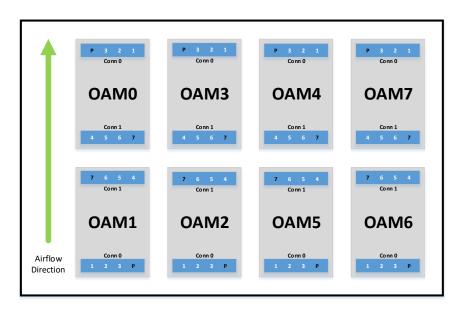

|   | 9.1  | Module ID                                                           | 53 |

|   | 9.2  | Interconnect Topology                                               | 54 |

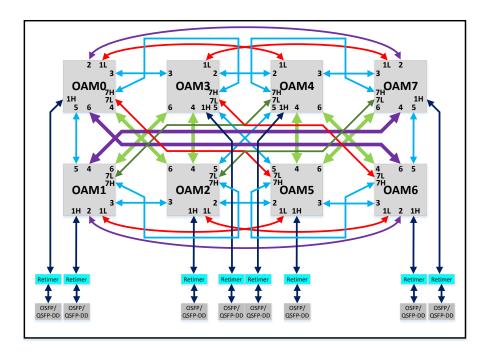

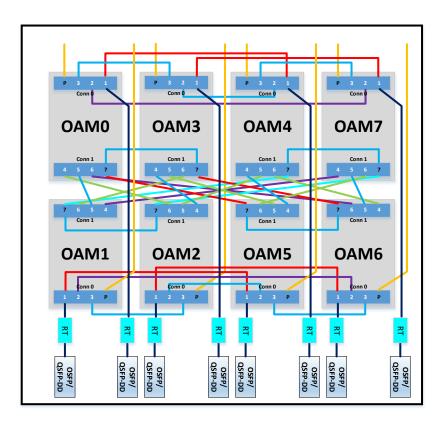

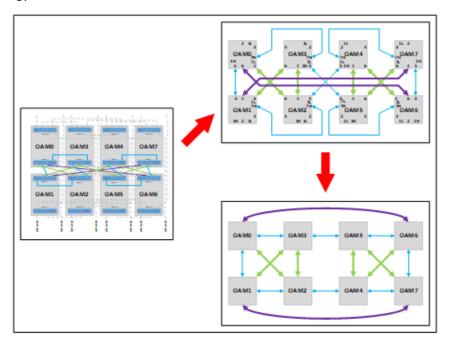

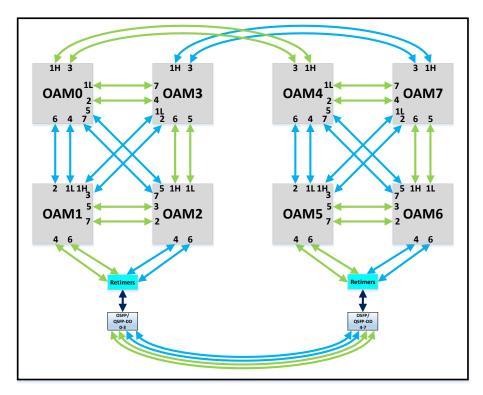

|   | 9.2. | Combined Fully Connected and 6-port Hybrid Cube Mesh Topology       | 54 |

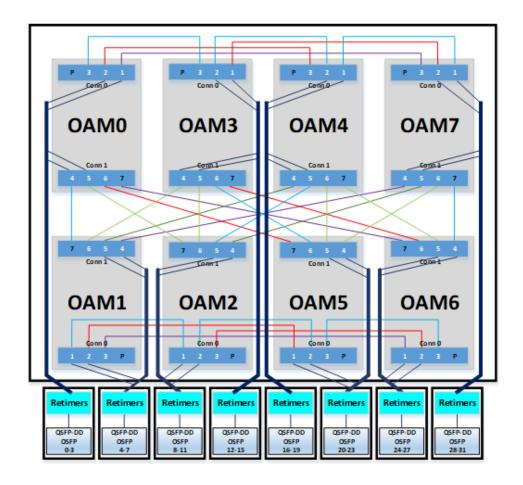

|   | 9.2. | 8-port Hybrid Cube Mesh Topology                                    | 57 |

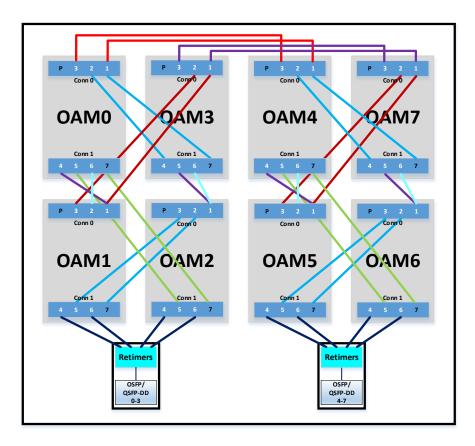

|   | 9.2. | 3 11-Port (7+4) FC/Retimer Topology (Fully Connected + 4 Scale Out) | 58 |

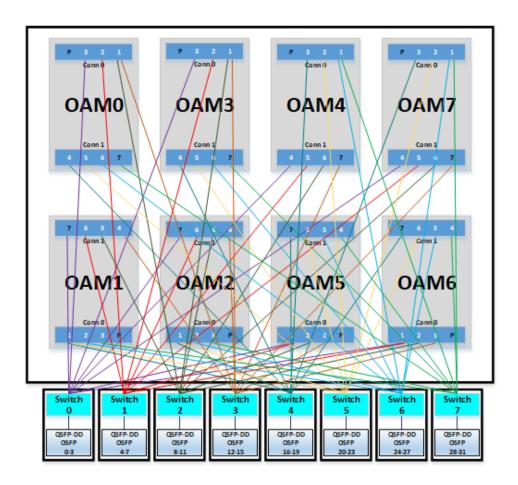

| 9.   | 2.4   | 8-Port Switch-Based Topology59           |

|------|-------|------------------------------------------|

| 9.3  | LI    | NK_CONFIG[4:0]61                         |

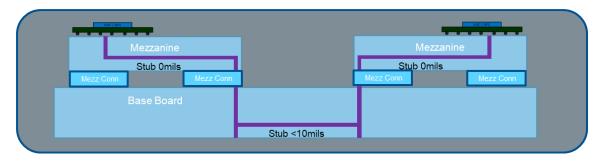

| 9.4  | 0     | AM Interconnect PCB Topology61           |

| 10   | OAN   | VI reference system design62             |

| 11   | OAN   | M Management and Security Requirements63 |

| 11.1 | . N   | Nanagement Interface63                   |

| 11.2 | . Se  | ensor Reporting63                        |

| 11.3 | B E   | rror Monitoring/Reporting64              |

| 11.4 | l Fi  | irmware Update64                         |

| 11.5 | P     | ower Capping65                           |

| 11.6 | 5 FI  | RU Information65                         |

| 11.7 | ' IC  | Calibration65                            |

| 11.8 | 8 0   | AM Security Requirements66               |

| 13   | 1.8.1 | Secure Boot66                            |

| 13   | 1.8.2 | Recovery67                               |

| 13   | 1.8.3 | Debug Capabilities67                     |

| 13   | 1.8.4 | Attestation67                            |

| 12   | Envi  | ironmental68                             |

| 12.1 | . E   | nvironmental Requirements68              |

| 12.2 | 2 R   | egulation68                              |

| 13   | Vers  | sion History69                           |

#### 1 License

Contributions to this Specification are made under the terms and conditions outlined in Open Web Foundation Contributor License Agreement ("OWF CLA 1.0") ("Contribution License") by:

AMD, Baidu, Broadcom, Graphcore, H3C, Inspur, Intel, Intel Habana, Luxshare, Meta, Microchip, Molex, Nallasway, Supermicro, TE, Wiwynn, ZT Systems

Usage of this Specification is governed by the terms and conditions outlined in the Open Web Foundation Final Specification Agreement ("OWFa 1.0").

Note: The following clarifications, which distinguish technology licensed in the Contribution License and/or Specification License from those technologies merely referenced (but not licensed), were accepted by the Incubation Committee of the OCP:

None.

NOTWITHSTANDING THE FOREGOING LICENSES, THIS SPECIFICATION IS PROVIDED BY OCP "AS-IS", AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO, OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION, INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 2 Compliance with OCP Tenets

# 2.1 Openness

OAM Base Specification is an open standard with joint contribution across Hyperscalers, ODMs, component suppliers, and connector vendors.

# 2.2 Impact

OAM Base Specification defines common form factor for AI/HPC accelerator modules and greatly cut down design cycle time and resources for companies adopting the standard.

OAM has been widely adopted by Hyperscalers, CSPs, and OEMs.

#### 2.3 Scale

OAM Base Specification defines GPU/ASIC power consumption up to 1000W with form factor and connector selection to support future advanced ASIC package technology and power delivery solution.

# 2.4 Sustainability

OAM Base Specification defines liquid cooling implementation to improve data center facility PUE and WUE.

OAM Base Specification defines power delivery solution with dual power entries and multiple stack height connector to improve power delivery efficiency for AI/HPC GPU or ASIC at 1KW TDP.

# 3 Acknowledgements

We want to acknowledge all the OCP OAI Workstream members for their contributions to this specification: The incredible collaboration between customers, accelerator manufacturers, system developers, and industry partners shows how Open Compute develops industry-standard form factors and specifications that benefit all its members.

We would especially like to thank **AMD**, **Boyd**, **CoolerMaster**, **H3C**, **Intel**, **Intel Habana**, **Meta**, **Molex**, **and Wiwynn** for their extra efforts in putting this specification together.

#### 4 Overview

Artificial Intelligence (AI) applications are rapidly evolving and producing an explosion of new types of hardware accelerators for Machine Learning (ML), Deep Learning (DL), and High-performance Computing (HPC).

Different implementations target similar requirements for power/cooling, robustness, serviceability, configuration, programming, management, debug, inter-module communication to scale-up, and input/output bandwidth to scale out.

To take advantage of the available industry-standard form factors to reduce the required time and effort in producing suitable solutions, various implementations have selected the PCIe CEM form factor as a quick market entry.

Such solutions are not optimized for the upcoming AI workloads, which require ever-growing bandwidth and interconnect flexibility for data/model parallelism.

The state-of-the-art applications require multiple cards in a system with various inter-card links running at highspeed interconnect bandwidth between cards.

Using the PCIe CEM form factor to meet such interconnect requirements poses several challenges. These include excessive signal insertion loss from ASIC to PCIe connectors and baseboard, inter-card cabling complexity reducing robustness and serviceability, and limiting the supported inter-ASIC topologies.

This base specification outlines an interoperable, modular hierarchy based on the OAM form factor (OCP Accelerator Module), an interconnect Baseboard, a Tray, and a Chassis. It enables flexible high-speed interconnect topologies for multi-ASIC solutions,

- OAM (various accelerators)

- Universal Baseboard (interconnecting topologies between accelerators, hosts, and other IO devices for scale up and scale out)

- OAI Tray (a means for ease of field replacement and serviceability)

- OAI Chassis (an outline for a collection of Trays and input/output resources to scale out)

Based on this base specification, various design and product implementations may maintain interoperability while offering enhancements in each hierarchy level.

We invite open contributions in the following areas:

- 1. Base specification (OCP Accelerator Infrastructure Sub-Project Specification)

- 2. Design specification (This document, detailed description of alternative, interoperable components which meet the base specification)

- 3. Products (schematic, layout, mechanical/thermal solutions, and firmware/software to realize the above designs)

# 4.1 Scope

The OAM base specification defines the form factor, standard specifications for a compute accelerator module, and a compliant baseboard design enabling interoperability across multiple ASIC or GPU-based mezzanine modules and baseboard design interfaces.

The OAM form factor facilitates scalability across accelerators by simplifying the system solution when interconnecting communication links among modules compared to a PCIe Add-in card form factor.

# 4.2 Acronyms

| Acronym | Definition                              |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|

| ASIC    | Application Specific Integrated Circuit |  |  |  |  |

| OAM     | OCP Accelerator Module                  |  |  |  |  |

| BGA     | Ball Grid Array                         |  |  |  |  |

| BMC     | Baseboard Management Controller         |  |  |  |  |

| TDP     | Thermal Design Power                    |  |  |  |  |

| EDP     | Excursion Design Power                  |  |  |  |  |

| GPU     | Graphic Processing Unit                 |  |  |  |  |

| MPN     | Manufacturing Part Number               |  |  |  |  |

| DXF     | Drawing eXchange Format                 |  |  |  |  |

| PCBA    | Printed Circuit Board Assembly          |  |  |  |  |

| UBB     | Universal Baseboard                     |  |  |  |  |

| OAI     | Open Accelerator Infrastructure         |  |  |  |  |

# **5 High-Level Specification for the OCP Acceleration Module**

| Module Dimension                          | 102mm x 170mm                                                             |

|-------------------------------------------|---------------------------------------------------------------------------|

| Module Power/Input<br>Voltage             | Supports up to 1000W, using 44V-59.5V DC as input power                   |

|                                           | 2* Molex Mirror Mezz Pro Connectors (MPN: 218910-1115 or 218916-<br>1115) |

| Connectors                                | Stack height 5mm ± 0.15 or 8 mm ± 0.15                                    |

|                                           | Differential pair Impedance: 90ohm ± 5%                                   |

| Host Interface                            | One or two x16 host links. E.g., PCIe Gen5/6 x16, or alternate protocols. |

| Module to Module                          | Up to 7 Links per module, each link has up to x16 lanes                   |

| Interconnect Links                        | Each link may be able to be configured into sub-links.                    |

| Bottom stiffener height (including Mylar) | 5.15mm (MAX) or 8.15mm (MAX)                                              |

# 6 OAM Mechanical Specifications

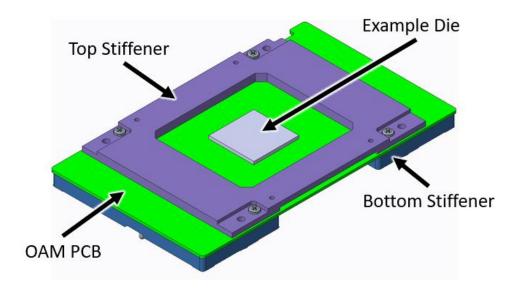

This section describes the OAM form factor. It uses a single accelerator ASIC on the module as an example to illustrate the mechanical specifications. The top and bottom stiffeners may be different if the modules have multiple accelerator ASICs.

Please refer to 2D DXF and 3D files for further details. 2D DXF and 3D files are in the contribution package, with relevant reference drawings to mechanical components. Please note that some OAM features call out as required, but others are for reference.

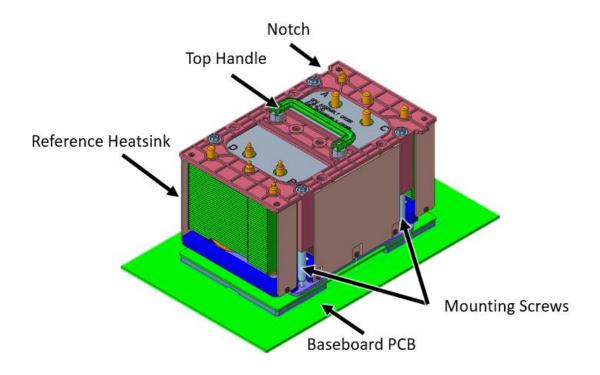

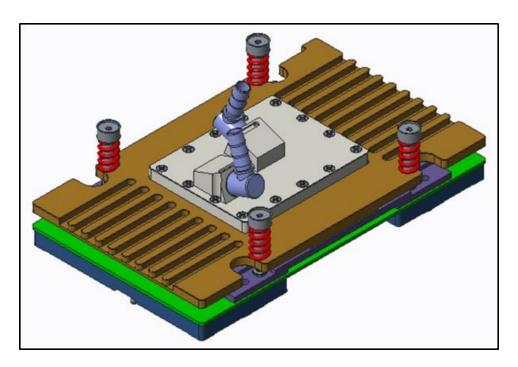

Figure 1 OAM isometric view

#### 6.1 Module PCBA Form Factor

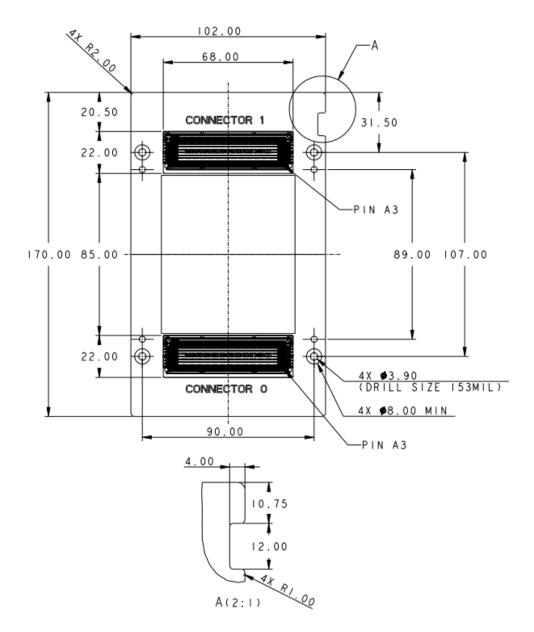

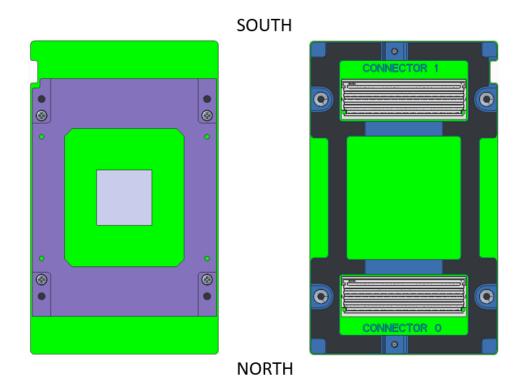

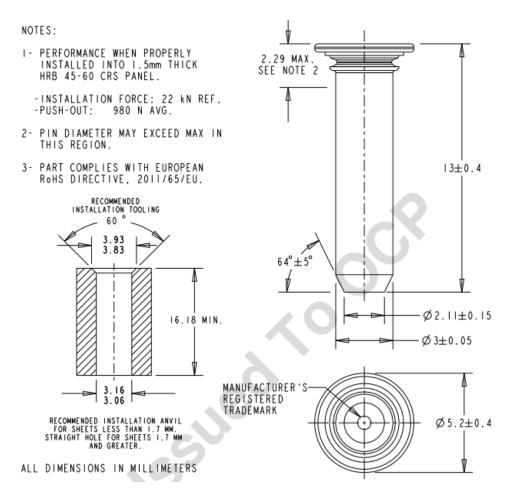

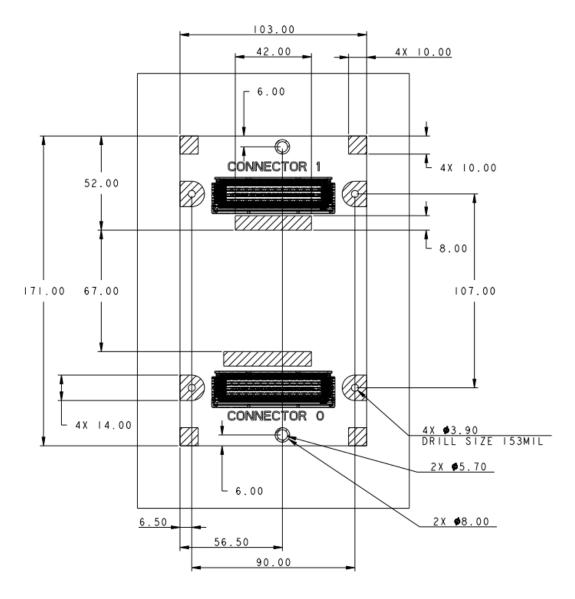

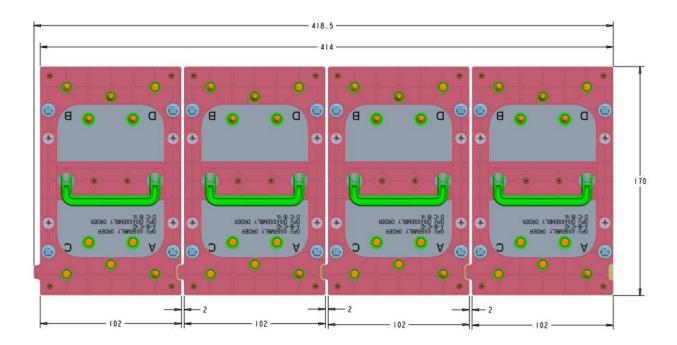

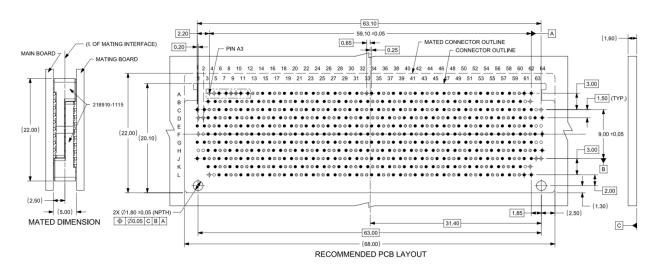

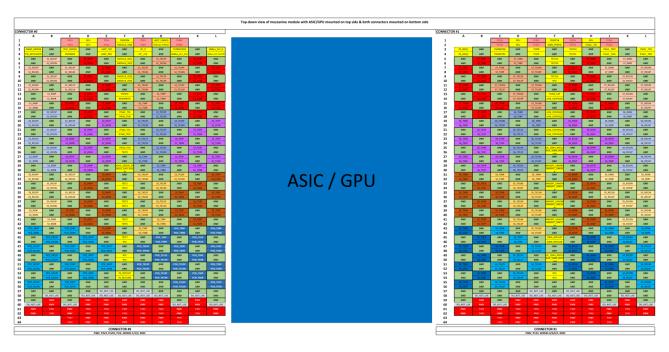

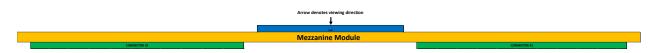

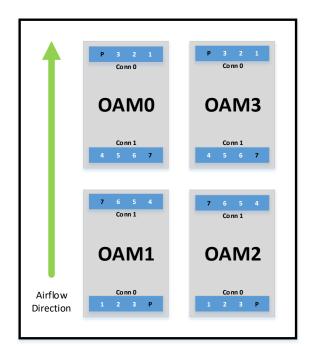

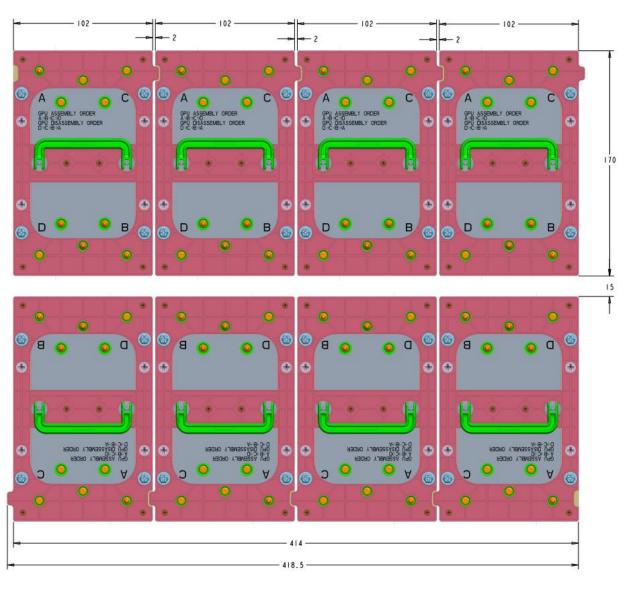

This section covers the required and recommended dimensions of the module PCBA and its parts. Figures 2 and 3 illustrate the OAM form factor and dimensions, with all the measurements in Figure 2 required. It is a 102mm x 170mm PCB size, Mezzanine Connectors on the bottom side, and the accelerator on the top side. The connector to connector pitch is 107mm. Four NPTH mounting holes attach the module to a corresponding bolster plate secured below the system PCB. These mounting holes should provide clearance for an M3.5 screw with enough thread length to secure the bottom stiffener. There is a notch located near the southwest corner of the board, adjacent to Connector 1. For connector orientation, see Figure 4 Top and bottom views of the OAM Assembly.

Figure 2 OAM Form Factor Dimensions, Bottom View

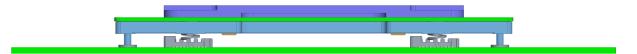

Figure 3 OAM Form Factor, Side View with System Baseboard

Figure 4 Top and bottom views of the OAM Assembly

#### **6.2 Mezzanine Connector**

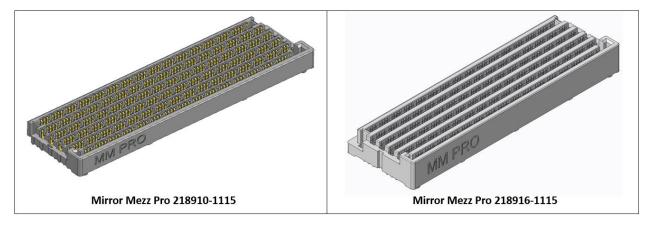

There are two versions of Molex Mirror Mezz Pro, MPN 218910-1115 and 218916-1115. Molex Mirror Mezz Pro is the PCB to PCB interconnect solution supported by the OAM form factor. Mirror Mezz Pro is a highspeed differential pair-based mezzanine connector in a footprint-identical genderless plug and receptacle part for module and baseboard. Figure 5 Mirror Mezz Pro 218910-1115 and 218916-1115 are provided courtesy of Molex.

- Stack height: 5mm (218910-1115 engages with 218910-1115 on UBB).

- Mating Force: 0.50N/pin Max, total 344.0N MAX. Data on mate forces of the 218910-1115 connector is in Table 1.

- Unmating force: 0.045N/pin MIN, total 31.0N MIN. Data on the unmate force of the 218910-1115 connector is in Table 1.

- 172 Total Differential Pairs, of which 161 are fully ground shielded (non-orphan).

The specification of another version of Mirror Mezz Pro 218916-1115 are listed below.

- Stack height: 8mm (218916-1115 engages with 218910-1115 on UBB).

- Mating Force: 0.50N/pin Max, total 344.0N MAX. Data on mate forces of the 218916-1115 connector is in Table 1.

- Unmating force: 0.045N/pin MIN, total 31.0N MIN. Data on the unmate force of the 218916-1115 connector is in Table 1.

- 172 Total Differential Pairs, of which 161 are fully ground shielded (non-orphan).

Figure 5 Mirror Mezz Pro 218910-1115 and 218916-1115

#### 6.2.1 Mate/Unmate Force Data

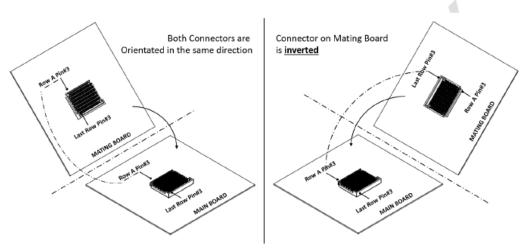

The mating connectors will be vertically inverted when mated.

Mating board flip over the top (calendar) VS page turning (book) style. For both style, the mating board connector will be vertically inverted when mated.

For both Layouts above, Main Board Row A Pin #3 connects to Mating Board Connector Last Row Pin #3 Take note of the Mating Board connector orientation

Figure 6 Mirror Mezz Pro Connector Mating

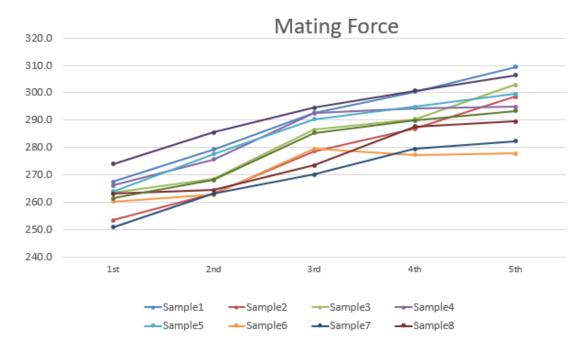

The mate and unmate forces provided in the product specification are conservative. The specific 218910-1115 and 218916-1115 connectors that the OAM uses has mate/unmate forces more in line with those found in Table 1 and in Figure 7. The mating force per pin trends upwards for the initial 5 cycles before settling back towards the average of 0.41N/pin.

Table 1 Mate/Unmate Averaged Data for both Mirror Mezz Pro 218910-1115 and 218916-1115

Mate and Un-mate Force (unit:N)

| Unit:N          | Cycle    | 1st   | 2nd   | 3rd   | 4th   | 5th   | Max   | Min   | Ave   |

|-----------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

|                 | Sample1  | 267.5 | 279.4 | 292.8 | 300.4 | 309.5 |       |       |       |

|                 | Sample2  | 253.5 | 263.1 | 278.6 | 286.9 | 298.5 |       |       |       |

|                 | Sample3  | 263.4 | 268.5 | 286.5 | 290.3 | 303.0 |       |       |       |

|                 | Sample4  | 266.1 | 275.7 | 292.6 | 294.4 | 294.9 |       |       |       |

| Mating Force    | Sample5  | 264.0 | 277.6 | 290.3 | 294.9 | 299.5 | 309.5 | 250.9 | 280.7 |

| Mating Force    | Sample6  | 260.2 | 262.8 | 279.5 | 277.4 | 277.9 | 303.3 | 250.9 | 200.7 |

|                 | Sample7  | 250.9 | 263.1 | 270.2 | 279.5 | 282.3 |       |       |       |

|                 | Sample8  | 263.2 | 264.4 | 273.5 | 287.7 | 289.5 |       |       |       |

|                 | Sample9  | 261.4 | 268.1 | 285.4 | 289.8 | 293.4 |       |       |       |

|                 | Sample10 | 274.0 | 285.5 | 294.5 | 300.8 | 306.4 |       |       |       |

|                 | Sample1  | 151.0 | 161.5 | 173.6 | 184.5 | 185.4 |       | 151.0 | 176.1 |

|                 | Sample2  | 162.8 | 176.3 | 181.1 | 181.4 | 180.9 | 185.6 |       |       |

|                 | Sample3  | 162.7 | 179.1 | 182.5 | 184.8 | 185.6 |       |       |       |

|                 | Sample4  | 159.7 | 176.6 | 182.1 | 182.6 | 184.9 |       |       |       |

| Jn-mating Force | Sample5  | 169.0 | 179.4 | 184.0 | 184.7 | 183.9 |       |       |       |

| on-maing Force  | Sample6  | 159.8 | 170.1 | 172.5 | 173.6 | 176.3 | 103.0 | 131.0 |       |

|                 | Sample7  | 160.0 | 173.1 | 176.6 | 178.1 | 178.6 | 1     |       |       |

|                 | Sample8  | 161.8 | 177.0 | 177.3 | 180.5 | 181.6 |       |       |       |

|                 | Sample9  | 162.1 | 175.2 | 179.4 | 181.1 | 181.8 |       |       |       |

|                 | Sample10 | 168.3 | 182.3 | 185.3 | 185.3 | 184.8 |       |       |       |

Figure 7 Measured Mate Force per Pin for both Mirror Mezz Pro 218910-1115 and 218916-1115

# 6.3 OAM Top Stiffener

The reference model of OAM top stiffener is for reference only, and dimensions may be changed or adjusted to accommodate the specific application and board layout of the OAM design.

#### 6.4 OAM Bottom Stiffener

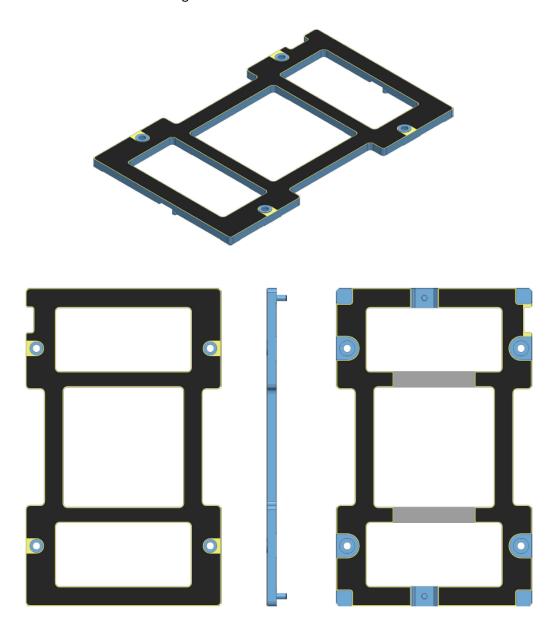

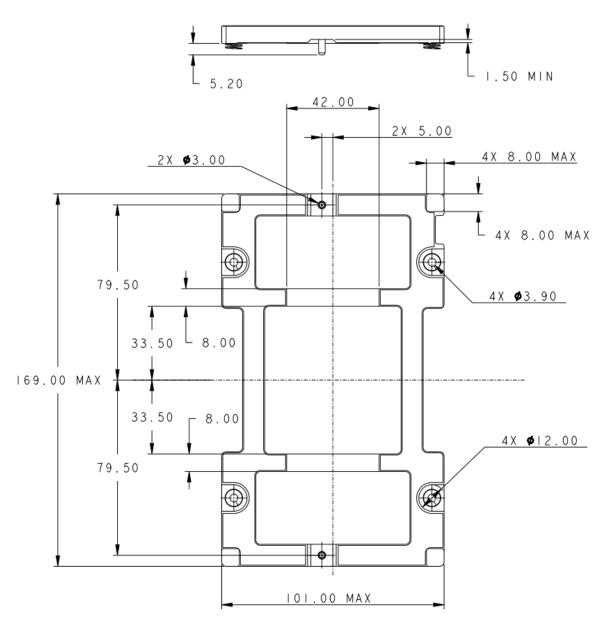

The reference model of OAM bottom stiffener in Figure 8 Bottom Stiffener Reference Design and dimensions are shown in Figure 9 Bottom Stiffener Dimensions. The bottom stiffener must accommodate the SMT nuts sizes shown in Figure 16 SMT Receiving Nut for Baseboard. Other features and dimensions of the bottom stiffener shown in the reference model are optional and can be adjusted based on the needs of the OAM design.

**Figure 8 Bottom Stiffener Reference Design**

**Figure 9 Bottom Stiffener Dimensions**

#### 6.4.1 Tolerance Stack-up of Bottom Stiffener

Standoff height as recommended by Molex for the Mirror Mezz Pro Connector is  $5 \, \text{mm} \pm 0.15 \, \text{mm}$  or  $8 \, \text{mm} \pm 0.15 \, \text{mm}$ , depending on the version of Mirror Mezz Pro. This tolerance may be difficult to attain using an insulator-adhesive-stiffener-adhesive-insulator stack, so it is highly recommended that pockets be machined into the stiffener to account for the tolerances of the insulator and adhesive (see reference design CAD for further details). With a stiffener only stack, 0.15 mm should be easily attainable.

Figure 10 Tolerance Stack-up of Bottom Stiffener

#### 6.4.2 Alignment Pins

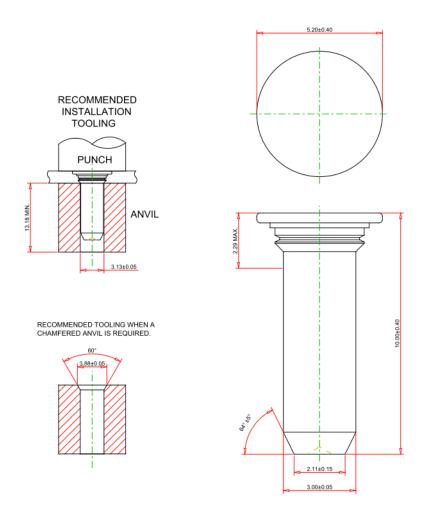

There are two alignment pins required on the bottom stiffener of the OAM, intended as guidance features and an additional keying feature for the module (see Section 6.5 for more details). The pins are 3mm diameter. For stacking height 5mm, the alignment pin is with a length of 10mm measured from the bottom of the OAM PCB. For stacking height 8mm, the alignment pin is with a length of 13mm measured from the bottom of the OAM PCB. Note that since there may be components on the bottom side of the PCB, if the stiffener pocket in this area, the total length of the pin will be shorter. The minimum thickness of the stiffener is 1mm in these areas, as recommended. Figure 11 and 12 show examples of the possible alignment pins. Note that the length will vary depending on the specifically chosen geometry of the bottom stiffener.

MPN: PEM TPS-3mm-10 or equivalent

Figure 11 Alignment pin example of 5mm Stacking Height

Figure 12 Alignment pin example of 8mm Stacking Height

#### 6.4.3 EMI Gaskets / Pads

The bottom stiffener has two defined areas of 8x42mm size, reserved for the placement of fabric-over-foam gaskets. This area is designed to have a 0.5mm depth, and the gasket defined should have a 6x40mm footprint, with a 1mm height. It provides a 50% nominal compression and solid grounding to the baseboard (equivalently designed ground pad).

MPN: Laird 4Y03PC51H00158 or equivalent

Figure 13 Fabric-over-foam Gasket Locations (brown)

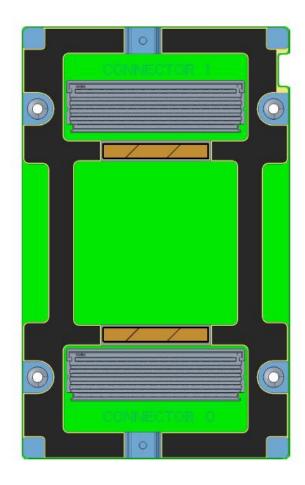

#### 6.4.4 Die Springs

Due to the mate and unmate forces of Mirror Mezz Pro connectors are high (see Section 6.2.1). Die springs are to be used to assist with the de-mate. It is strongly suggested for OAM vendors to use this reference spring in their design.

However, an equivalent spring shall have a spring constant of at least 70N/mm and at least 2.5mm compression. The inner diameter shall be 4.2mm, and the outer diameter shall be 7.8mm. These springs fit into 8mm diameter counterbores of 4mm depth in the bottom stiffener. The installation method uses glue (3M DP810 or equivalent), applied with a maximum thickness of 0.1mm.

MPN: Timson WG774265 or equivalent

| D (mm)                | d (mm)               | L (mm)              | a (mm)                | F (mm)                | K (N/mm) |

|-----------------------|----------------------|---------------------|-----------------------|-----------------------|----------|

| $7.8^{+0.05}_{-0.20}$ | $4.2^{+0.1}_{-0.15}$ | $6.5^{+0.2}_{-0.2}$ | $3.6^{+0.15}_{-0.15}$ | $2.9^{+0.35}_{-0.35}$ | 78.6±10% |

Figure 14 Die Spring dimensions and drawing

Table 2 Spring constant and free length of die springs, shown compared to cycle count

|     | Sample I |        | Sample 2 |        | Sample 3 |        | Sample 4 |        | Sample 5 |        |

|-----|----------|--------|----------|--------|----------|--------|----------|--------|----------|--------|

|     | L        | K      | L        | K      | L        | K      | L        | K      | L        | K      |

|     | (mm)     | (N/mm) |

| ı   | 6.48     | 81.87  | 6.44     | 80.88  | 6.48     | 82.12  | 6.45     | 80.20  | 6.46     | 80.70  |

| 2   | 6.47     | 81.23  | 6.43     | 79.80  | 6.47     | 81.86  | 6.44     | 79.98  | 6.46     | 80.58  |

| 3   | 6.47     | 81.01  | 6.42     | 79.84  | 6.47     | 81.33  | 6.44     | 79.96  | 6.45     | 80.48  |

| 4   | 6.46     | 80.95  | 6.42     | 79.70  | 6.46     | 81.20  | 6.44     | 79.80  | 6.45     | 80.46  |

| 5   | 6.46     | 80.95  | 6.41     | 79.37  | 6.46     | 81.17  | 6.43     | 79.68  | 6.44     | 80.28  |

| 6   | 6.46     | 80.90  | 6.41     | 79.22  | 6.46     | 81.13  | 6.43     | 79.40  | 6.44     | 80.29  |

| 7   | 6.46     | 80.79  | 6.40     | 79.31  | 6.45     | 80.97  | 6.42     | 79.52  | 6.43     | 80.12  |

| 8   | 6.45     | 80.77  | 6.40     | 79.16  | 6.45     | 81.17  | 6.42     | 79.48  | 6.43     | 80.02  |

| 9   | 6.45     | 80.76  | 6.39     | 79.11  | 6.43     | 80.98  | 6.41     | 79.47  | 6.42     | 79.90  |

| 10  | 6.44     | 80.68  | 6.39     | 79.02  | 6.43     | 80.91  | 6.41     | 79.38  | 6.42     | 79.93  |

| Avg | 6.46     | 80.99  | 6.41     | 79.54  | 6.46     | 81.28  | 6.43     | 79.69  | 6.44     | 80.28  |

## 6.5 Baseboard Keep out Zone & Grounding Pads

The below figure shows the baseboard outline (top side view) required to accommodate this module. All cross-hatched areas need to be grounded except for the four corners 10x10 square holes. The 10x10 square holes in the corners are highly recommended for being grounded. Additionally, it is recommended to route high-speed traces away from mounting hole areas due to large compression forces from the die spring.

Figure 15 Baseboard KOZ and Grounding Pad Dimensions

#### 6.5.1 SMT Nut

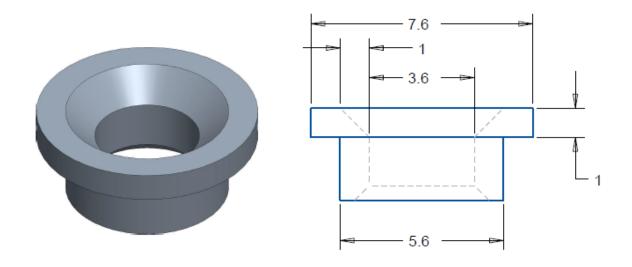

The SMT nuts with the dimensions shown in Figure 16 are to be soldered to the baseboard with 5.7mm diameter holes. These nuts provide the mating features to the alignment pins on the bottom stiffener of

the OAM. Clearance of the 3mm pins in the 3.6mm nuts means that the module will come within 0.3mm of its final position.

MPN: Ray Home 1000401319 or equivalent

Figure 16 SMT Receiving Nut for Baseboard

#### 6.5.2 Component Keep-out Zone

The baseboard has a component keep-out zone of 103x171mm, as shown in Figure 15 Baseboard KOZ and Grounding Pad Dimensions.

#### 6.5.3 Grounding Pads

As with the bottom stiffener, the baseboard has two grounding pads of size 8x42mm, for the EMI fabric-over-foam gaskets on the stiffener to provide good contact. Refer to Section 6.4.3 for gasket MPN and description.

# 6.6 Recommended Alignment Features

There are three stages of engagement when installing the OAM to the system.

Stage 1: Notch in top of heatsink providing visual guidance and orientation reference. The reference design shows 2mm clearances.

Figure 17 Top view of four adjacent OAM with heatsinks

Stage 2: Alignment pins, two 3mm pins from the OAM into two 3.6mm SMT nuts on the baseboard.

Figure 18 Side view (exploded) showing alignment pins being received by 1mm tall SMT nuts

Stage 3: Connector housing built-in engagement (Molex Mirror Mezz Pro gather ability: 0.76mm).

Figure 19 Side view (exploded) showing mezzanine connectors doing final alignment

# 6.7 Reference Heatsink Design

An air-cooled solution recommends TDP equal or less than 600W modules. For modules that are over 600W, other cooling solution is recommended such as liquid cooling.

Below figure shows the reference model of the heatsink with OAM assembly.

Figure 20 Reference Model of Heatsink with OAM Assembly

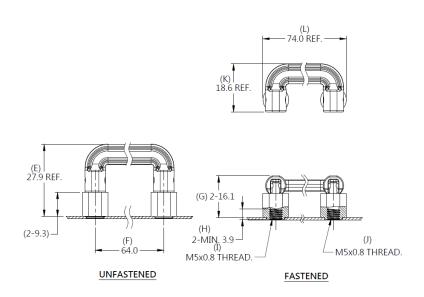

#### 6.7.1 Top Handle

Due to the size and bulk of the heatsink and module assembly, a handle is recommended. The reference design uses a folding handle. This handle screws into a sheet metal panel attached to the heat sink base with six M2.5 flathead screws. This attachment method allows the load to transfer through the more rugged base instead of the delicate heat sink fins.

MPN: Fivetech 62-57P-064-7-02-5 or equivalent

Figure 21 Dimensioned Smart Folding Handle from Reference Design

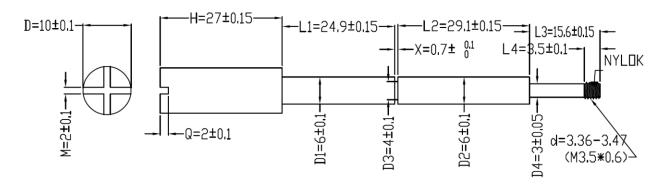

#### 6.7.2 Long Screw Attachment

A set of four M3.5, spring-loaded, Phillips head long screws are used to attach the module to the baseboard. Note that the reference screw provided is simply a reference and that L3 and L4 will need to be adjusted based on the thicknesses of the baseboard and bolster plates. However, these mounting screw locations are fixed per the requirements of the OAM board layout and the baseboard layout. Each screw clears the top stiffener, mezzanine PCB, bottom stiffener (including the die spring), and the baseboard to screw directly into the bolster plate below the baseboard PCB. It is recommended that the OAM be attached to the baseboard by torquing the screws in a diagonal pattern.

MPN of Long Screw: Wujiang Screw MDCM0359733N or similar MPN of Spring for Long Screw: Surpassing Hardware Spring FDJG7004010 or similar

Figure 22 Drawing of Wujiang Screw MDCM0359733N

# 7 Thermal Specification

The thermal requirements are applicable to air-cooled conditions by default, except where a different cooling approach is specifically called out.

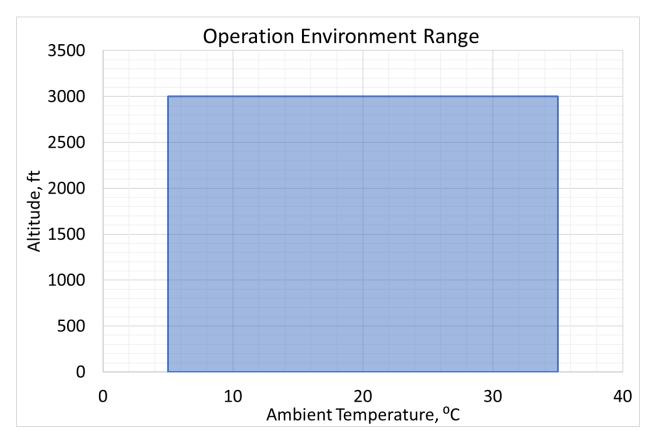

#### 7.1 Environmental Conditions

The thermal and cooling solution should dissipate heat from the components when the module operates at its thermal design power to meet the thermal reliability requirement. The module should be able to work in the following environmental conditions without any throttling or thermal issues:

- Ambient temperature: 5°C to 35 °C

- Approach temperature: 10°C to 48 °C, considering shadowing other components

- Altitude: sea level to 3000 ft\*, without temperature deration

- Relative Humidity: 20% to 90%

- Cold boot temperature: the module should be able to boot and operate at an initial temperature of 10°C

In addition, the module should remain unaffected at a non-operational storage temperature range of - 20°C to 85°C.

**Figure 23 Module Operation Ambient Temperature**

<sup>\*</sup>An extended altitude range of up to 6000ft is recommended.

# 7.2 Temperature Report

#### 7.2.1 Temperature Sensors

The module reports readings of ASIC temperature sensor and HBM temperature sensor to support software or hardware throttling, shutdown, and drive fan speed through BMC. The sensors should be located or calibrated to:

- Always report the hottest junction temperature in the component

- Keep accuracy within ±3°C

Lower temperature limit, non-critical temperature limit, and critical temperature limit should be defined for those temperature sensors to support throttling or shutdown features.

#### 7.2.2 Remaining Components

For the remaining components that are not monitored by temperature sensors or not included in fan speed control (FSC), their cooling solutions should be appropriately designed such that:

- Before ASIC or Memory temperature readings reach throttling thresholds, they will be maintained below the temperature limits.

- When any ASIC or Memory temperature reading reaches a throttling threshold but not the hardware shutdown limit, these components will remain functional to support the reduced functionality of the module.

#### 7.3 Thermal module information

To enable the module with appropriate cooling solutions, the supplier will provide the following thermal info for each product model:

- ASIC & Memory (HBM or DRAM) junction temperature limit.

- ASIC & Memory (HBM or DRAM) junction to surface/case temperature correlations.

- Connector surface temperature limit.

- ASIC & Memory (HBM or DRAM) junction temperature range at nominal operation conditions.

# 7.4 Heatsink Assembly

The module will meet these requirements to minimize the complexity of assembly, servicing, and risk of failure:

- Only one replaceable heatsink assembly (primary heatsink) is needed for the module, which can be swapped in the field.

- The other heatsink parts (i.e., secondary heatsinks) and thermal interface materials will come with the module and do not need replacement over the module lifetime.

Reliability test reports will be provided to validate the lifetime of the thermal interface materials. Shock and Vibration test reports will be provided to validate the robustness of the module assembly.

#### 7.5 Thermal Recommendation

#### 7.5.1 Airflow Budget

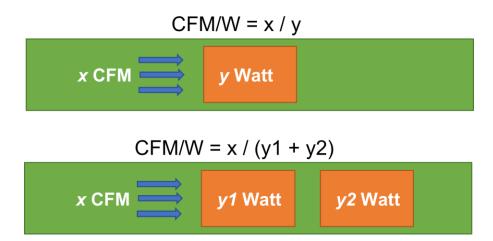

Considering OAM module meets the limits on the air delivery/removal capabilities of typical infrastructures, it is recommended that the OAM module operates with a complete performance at or below an airflow/power ratio of 0.158 CFM/W, with ambient temperature up to 35°C at sea level, equivalent to an inlet/outlet air temperature increase of 20°F.

- For operation at altitude, the same air temperature difference of 22°F is recommended.

- For a single OAM that is shadowed by other components, the airflow/power ratio calculate with airflow through its heatsink and the module power

- For an OAM shadowing other components or multiple OAMs in serial, this calculation uses the airflow through the flow channel and the sum of the power of OAM modules and upstream components.

- For OAM modules with a power lower than 300W, an airflow/power ratio of 0.1 CFM/W or lower is usually achievable and recommended.

Figure 24 CFM per Watt

#### 7.5.2 Reference Heatsink Design

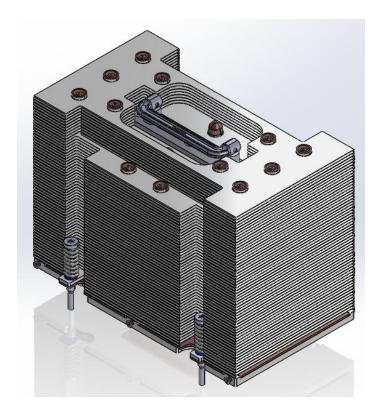

Refer to Figure 20 Reference Model of Heatsink with OAM Assembly. A reference heatsink design with 3D-VC technology is provided as in Figure 25.

Figure 25 OAM 2.0 Reference Heatsink Solution, 4U version

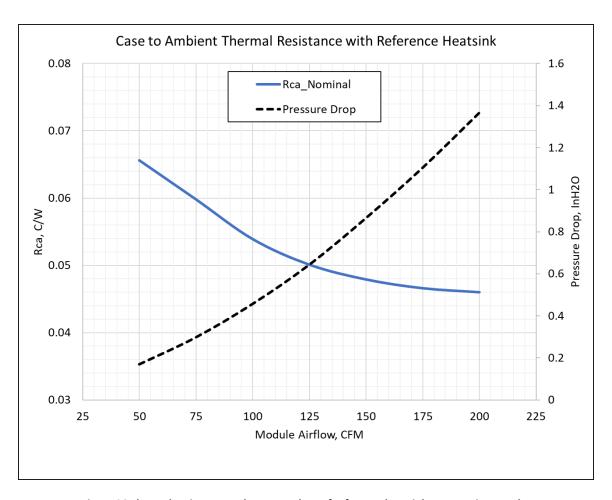

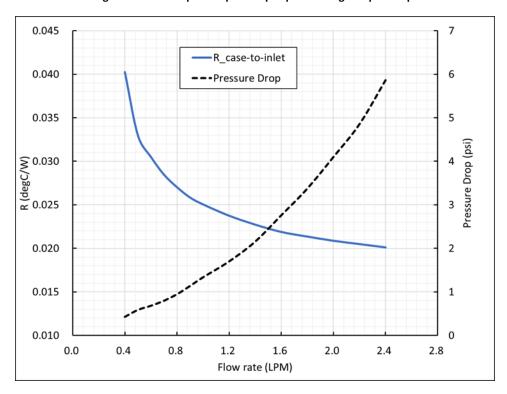

Performance of the reference heatsink is provided in Figure 26, the thermal resistance of which calculate based on:

$$R_{ca} = \frac{T_{case} - T_{LA}}{P_{die}},$$

Where  $T_{case}$  is the surface center temp of the heater,  $T_{LA}$  is the approaching temperature, and  $P_{die}$  is the heater's power, indicating the die instead of the total module power.

Die size and power density play an essential role in the thermal performance of the OAM module. The chart below provides expected thermal resistance and pressure drop of the heatsink with multiple assumptions applied. Those assumptions include nominal estimation of package size, power distribution and thermal interface material to the best of our knowledge, and performance on every real OAM2.0 product could vary due to different characteristics on any of the metrics mentioned. Results demonstrated in Figure 26 were based on TIM resistance of 0.2°C·cm²/W.

Figure 26 Thermal resistance and pressure drop of reference heatsink; assumptions apply.

Depending on model and application, the OAM may operate at a variety of power levels. However, air-cooled heatsinks may hit their performance limit due to the constraints on heat spreading and airflow delivery. Beyond a certain chassis height, fin size, and airflow rate, the improvement on the thermal resistance of the air-cooled heatsink becomes minimal.

For a reference OAM in a typical platform with 8x OAMs, shadowing layout, it is observed that the maximum module power that air cooling can support is approximately 600W. Beyond this power limit, advanced cooling solutions are recommended to keep its operation at the hotter part of the operational boundary condition range. These advanced cooling solutions would also be recommended for extended environment boundary conditions. This limit may vary for different products, depending on die size, power distribution, and junction temperature limits.

#### 7.5.3 Thermal Interface Material

The thermal interface material between the die (ASIC/HBM) and the primary heatsink should maintain a thermal conductivity of at least 3W/m×K through the end of its life.

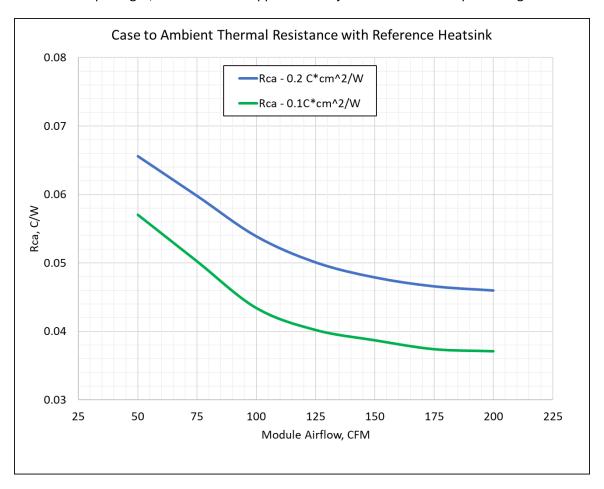

Depending on a variety of parameters, TIM could easily contribute  $0.1 \, ^{\circ}\text{C} \cdot \text{cm}^2/\text{W} \sim 0.2 \, ^{\circ}\text{C} \cdot \text{cm}^2/\text{W}$ , up to 50% of total thermal resistance.

The potentially achievable performance with better thermal interface resistance at 0.1°C·cm²/W is demonstrated in Figure 27. This may be achieved by using more suitable TIM choices, higher mounting pressure, or better warpage control of the package. Such resistance is usually observed on well-controlled lidded packages, where tradeoff applies due to junction-to-case temperature gradient.

Figure 27 Thermal resistance improvement due to better thermal interface between OAM package and heatsink

#### 7.5.4 Heatsink Installation

Many OAM modules use bare die design, which may be fragile and susceptible to an imbalance of pressure on its surface. The system integrator should contact the OAM supplier for the maximum static and dynamic pressure for the die to guide the installation of the primary heatsink to the module. The static mounting pressure should also be high enough to enable optimum performance of the TIM material.

We suggest installing the heatsink with multistage diagonal tightening sequences, for better balancing of the stress during the installation process. Customized jigs enabling simultaneous tightening of multiple screws may provide better yield rate.

The mounting pressure of the heatsink is determined by:

- Max pressure the package can sustain

- Min pressure the TIM needs to deliver enough performance

The mounting pressure may vary across the range of 20 ~ 60 psi for lidless OAM products, where lidded products could potentially sustain higher mounting pressure. We recommend an initial mounting pressure of 15~30 psi for engineering samples without assembly yield rate learnings.

## 7.6 Liquid Cooling Requirements

#### 7.6.1 Boundary Conditions

The OAM coldplate should be able to operate with coolant supply temperature across the spectrum of 15~50°C. Higher coolant temperatures within the spectrum are usually preferred for better hardware and facility efficiency, however the tradeoff would be cooling performance reduction. Accelerated test at higher temperatures are recommended to validate the design robustness and long term reliability. The coolants applicable to OAM cold plates are water with additives (treated water), or glycol-based liquids (PG25, etc.).

#### 7.6.2 Reliability Expectations

The OAM coldplate products should pass the reliability tests described in OCP Coldplate Development and Qualification, including:

- Hydrostatic Pressure Test

- Corrosion Test

- Dynamics Shock & Vibration test

- Temperature Cycling Test

It is recommended to have OAM coldplate products' annual failure rate below 0.3%.

#### 7.6.3 Reference Coldplate Design

An OAM 2.0 reference coldplate is demonstrated in Figure 28. With ideal package layout, coldplate design, quality control and thermal interface resistance of 0.1 °C·cm²/W, such coldplate is possible to deliver a case-to-inlet resistance of 0.02 °C/W in the best case, as shown in Figure 29.

Figure 28 An Example of Open Loop Liquid Cooling setup concept for OAM

Figure 29 Performance Curve of Reference Coldplate under ideal assumptions

#### 7.6.4 More Recommendations

More guidelines around OAI liquid cooling are provided in this publication:

- OAI Liquid Cooling Guidelines:

- https://www.opencompute.org/documents/oai-system-liquid-cooling-guidelines-in-ocptemplate-dec-7-2022-1-pdf

From OCP CE Coldpate group, there are also multiple guidelines published to help coldplate-based liquid cooling solution development for general hardware products:

- OCP ACS Cold Plate Leak Detection and Intervention

- https://www.opencompute.org/documents/acs-cold-plate-leak-detection-andintervention-white-paper-pdf-1

- OCP ACS Liquid Cooling Cold Plate Requirements

- https://www.opencompute.org/documents/ocp-acs-liquid-cooling-cold-platerequirements-pdf

- OCP Cold Plate Development and Qualification

- https://www.opencompute.org/documents/ocp-cold-plate-development-andqualification-with-integrated-comments-pdf

### 7.7 Consideration for Immersion Cooling

Immersion cooling is another advanced cooling technology that could bring performance benefit. However the impact on various aspects are still yet to be examined, including material compatibility, signal integrity, hardware design philosophy, reliability and serviceability, facility design, etc. A series of guidelines have been released by OCP CE Immersion group, to help development of immersion-based hardware products on multiple, but not all areas yet:

- Material Compatibility in Immersion Cooling

- https://www.opencompute.org/documents/material-compatibility-in-immersioncooling-document-version-1-0-nov-28-2022-1-pdf

- Base spec of immersion fluid

- https://www.opencompute.org/documents/ocp-base-specification-for-immersionfluids-20221201-pdf

- Design Guidelines for Immersion-Cooled IT Equipment

- https://www.opencompute.org/documents/design-guidelines-for-immersion-cooled-itequipment-revision-1-01-pdf

# 8 OAM Electrical Specification

#### 8.1 Electrical Connector

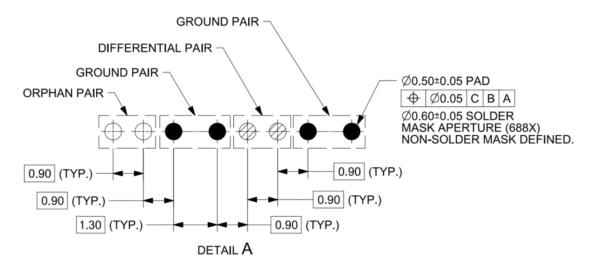

The module utilizes two 688pin Molex Mirror Mezz Pro connectors. It is a BGA attached connector. It supports bit rates up to 56Gbps NRZ or 112 Gbps PAM4 in a 90 Ohms nominal impedance ± 5% tolerance, making it compatible with support typical 85 Ohms based interfaces such as PCle Gen 5/6 as well as other 100 Ohms based high-speed interfaces. All power and I/O signals are routed through the two connectors down to the system baseboard. The system baseboard should connect these signals to the appropriate circuitry depending on the required feature sets. The below table lists the electrical requirements for the module connectors.

Table 3 Electrical Requirements for Molex Mirror Mezz Pro

| Items                                       | Mirror Mezz Pro           |

|---------------------------------------------|---------------------------|

| Data Rate Support                           | Up to 56G NRZ, 112G PAM4  |

| Connector Impedance                         | 90ohm ± 5%                |

| Differential pairs per two connectors       | 172 pairs                 |

| Pin Pitch                                   | 0.9mm and 1.3mm           |

| Current Rating per pin @85C (inclusive of   | 1A/pin after 20% derating |

| 30C T-rise) ambient temp, 1.5oz copper      |                           |

| Max Voltage Application                     | 30V AC (OAM supports 60V) |

| Connector insertion cycles                  | 100cycles                 |

| Withstand voltage                           | 500V min                  |

| Low-Level Contact Resistance (max initial): | 30mΩ for 5mm stack height |

| Insulation resistance                       | 1-MΩ min                  |

| Intra-pair skew                             | <=5 ps                    |

Figure 30 Mirror Mezz Pro Connector Footprint

Figure 31 Mirror Mezz Pro Connector Pin to Pin Pitch

## 8.2 OAM Connector Pinout Quadrants

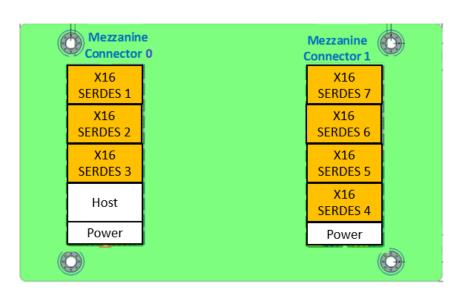

**Figure 32 Mezzanine Connectors Pinout Quadrants**

The OAM Connector 0 has the following interfaces:

- 54V/48V and 3.3V input power

- x16 SerDes to connect to host

- 3x16 SerDes for the accelerator to accelerator communication

- o x16 may split into sub-links like 2\* x8s or 4\* x4s or 16\*x1s.

- o If the ASIC or ASICs on the module only support x8 or x4 per SerDes, it should start from Lane0 from the SerDes, e.g., lane [7:0] or lane [3:0].

- We do not recommend lane reversal support on the baseboard due to modules having the option to be 1x16 links or 2x8 or 4x4 links.

- Other single-ended signals, like PRESNT#, SMBus, GPIOs etc.

The OAM Connector 1 has the following interfaces:

- 54V/48V and 12V (optional) input power

- Other single-ended signals like JTAG, GPIOs etc.

- Up to four SerDes for the accelerator to accelerator communication or other purposes:

- O SerDes 4, 5, 6, and 7 are up to x16 lanes which can split into x8s, x4s, or x1s.

- SerDes 7 may be defined for different use cases:

- This link could be the 7<sup>th</sup> SerDes for some cases to have a fully connected interconnect between the modules

- It could be the 2nd link to host for the ASIC(s) on the module, e.g., a full x16 link, 2x8, or 4x4 links.

- Or it could be a unique defined link by some ASICs. E.g., it could be a downstream port for the ASIC on the module.

### 8.3 OAM Pinout Description

The detailed pin mapping to connectors is in the separated spreadsheet (OAM\_Pinlist\_Pinmap\_r2.0\_v0.75.xlsx). This section only shows the pin list and description.

**Table 4 OAM Pinouts**

| Signal | IO Type<br>(Mezz<br>Module<br>Direction<br>POV) | Description                                                                                                                                                               | Voltage       | Total<br>Diff<br>Pair | Total<br>SE<br>pins | Conn0<br>or 1   | Note     |

|--------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|---------------------|-----------------|----------|

| P48V   | Power<br>Input                                  | 44V-59.5V main voltage<br>for 1000W.<br>40V min for lower power<br>(< 450W)<br>Split power pins to<br>Conn0 and Conn1.<br>Check with OAM<br>suppliers with 40V<br>support | 44V-<br>59.5V |                       | 100                 | Conn0/<br>Conn1 |          |

| P12V   | Power<br>Input                                  | 12V Board Infrastructure<br>Power. Up to 50W<br>(Optional)                                                                                                                | 12V           |                       | 8                   | Conn1           | Optional |

| P3V3   | Power<br>Input                                  | 3.3V Main Power. Up to 10W                                                                                                                                                | 3.3V          |                       | 6                   | Conn0           |          |

|                        |                                                    | Low voltage cutavit for                                                                                                                                                                                                                                                                    |      |    |   |       |  |

|------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|---|-------|--|

| PVREF                  | Power<br>Output                                    | Low voltage output for GPU/ASIC sideband I/O reference on motherboard components. Module should provision maximum 0.5A to be provided to motherboard. Vref can be any value between 1.2V to 3.3V set as per GPU/ASIC sideband I/O voltage. Each OAM supplier will specify the actual Vref. | Vref |    | 2 | Conn0 |  |

| PETp/n [15:0]          | Output                                             | PCIe or equivalent host link Transmit differential pairs. Module Transmit, Host Receive. Note: AC coupling caps must be placed on the motherboard side.                                                                                                                                    |      | 16 |   | Conn0 |  |

| PERp/n [15:0]          | Input                                              | PCIe or equivalent host link Receive differential pairs. Module Receive, Host Transmit. Note: AC coupling caps must be placed on the motherboard side.                                                                                                                                     |      | 16 |   | Conn0 |  |

| SERDES_1Tp/n<br>[15:0] | SerDes link 1 Transmit                             |                                                                                                                                                                                                                                                                                            |      | 16 |   | Conn0 |  |

| SERDES_1Rp/n<br>[15:0] | Input                                              | SerDes link 1 Receive differential pairs.                                                                                                                                                                                                                                                  |      | 16 |   | Conn0 |  |

| SERDES_2Tp/n<br>[15:0] |                                                    |                                                                                                                                                                                                                                                                                            |      | 16 |   | Conn0 |  |

| SERDES_2Rp/n<br>[15:0] | Input                                              | SerDes link 2 Receive differential pairs.                                                                                                                                                                                                                                                  |      | 16 |   | Conn0 |  |

| SERDES_3Tp/n[15:<br>0] | SerDes link 3 Transmit differential pairs. AC caps |                                                                                                                                                                                                                                                                                            |      | 16 |   | Conn0 |  |

| SERDES_3Rp/n<br>[15:0] | Input                                              | SerDes link 3 Receive differential pairs.                                                                                                                                                                                                                                                  |      | 16 |   | Conn0 |  |

| SERDES_4Tp/n[15:<br>0] | Output                                             | SerDes link 4Transmit<br>differential pairs. AC caps<br>must be placed on<br>Module/die (if required)                                                                                                                                                                                      |      | 16 |   | Conn1 |  |

| SERDES_4Rp/n   |        | SerDes link 4 Receive                     |       |    |       |         |   |

|----------------|--------|-------------------------------------------|-------|----|-------|---------|---|

| [15:0]         | Input  | differential pairs.                       |       | 16 |       | Conn1   |   |

| [13.0]         |        | SerDes link 5 Transmit                    |       |    |       |         |   |

| SERDES_5Tp/n   |        | differential pairs. AC caps               |       |    |       |         |   |

| [15:0]         | Output | must be placed on                         |       | 16 |       | Conn1   |   |

| [13.0]         |        | Module/die (if required)                  |       |    |       |         |   |

| SERDES_5Rp/n   |        | SerDes link 5 Receive                     |       |    |       |         |   |

| [15:0]         | Input  | differential pairs.                       |       | 16 |       | Conn1   |   |

| [13.0]         |        | SerDes link 6 Transmit                    |       |    |       |         |   |

| SERDES_6Tp/n   |        | differential pairs. AC caps               |       |    |       |         |   |

| [15:0]         | Output | must be placed on                         |       | 16 |       | Conn1   |   |

| [13.0]         |        | Module/die (if required)                  |       |    |       |         |   |

| SERDES_6Rp/n   |        | SerDes link 6 Receive                     |       |    |       |         |   |

| [15:0]         | Input  | differential pairs.                       |       | 16 |       | Conn1   |   |

| [15:0]         |        | SerDes link 7 Transmit                    |       |    |       |         |   |

| CEDDEC 3Tm/m   |        |                                           |       |    |       |         |   |

| SERDES_7Tp/n   | Output | differential pairs. AC caps               |       | 16 |       | Conn1   |   |

| [15:0]         |        | must be placed on                         |       |    |       |         |   |

| CEDDEC 70-/-   |        | Module/die (if required)                  |       |    |       |         |   |

| SERDES_7Rp/n   | Input  | SerDes link 7 Receive                     |       | 16 |       | Conn1   |   |

| [15:0]         |        | differential pairs. PCIe Reference Clock. |       |    |       |         |   |

| DE DEECLY /n   | Innut  |                                           |       | 1  |       | ConnO   |   |

| PE_REFCLKp/n   | Input  | 100MHz PCIe Gen 5 compliant.              |       | 1  |       | Conn0   |   |

|                |        | 100MHz PCle Gen 5                         |       |    |       |         |   |

| AUX_100M_REFCL | Innut  |                                           |       | 1  |       | Conn1   |   |

| Kp/n           | Input  | compliant Auxiliary Reference Clock.      |       | 1  |       | Conni   |   |

|                |        |                                           |       |    |       |         |   |

| AUX_156M_REFCL |        | 156.25MHz Auxiliary                       |       |    |       |         |   |

| Kp/n           | Input  | Reference Clock                           |       | 1  | Conn1 | Conn1   |   |

| KP/ II         |        | (Optional)                                |       |    |       |         |   |

|                |        | Downstream Reference                      |       | _  |       |         |   |

| DWN_REFCLKp/n  | Output | Clock. Vendor specific.                   |       | 1  |       | Conn1   |   |

|                |        | CEM Compliant PCIe                        | 2.01/ |    |       |         |   |

| PERST#         | Input  | Reset                                     | 3.3V  |    | 1     | Conn0   |   |

|                |        |                                           |       |    |       |         |   |

| WARMRST#       | Input  | Warm Reset                                | Vref  |    | 1     | Conn0   |   |

| WICHINIAAA     | Input  | vvaiiii Neset                             | VIEI  |    |       | COIIIIO |   |

|                |        |                                           |       |    |       |         |   |

| DWN_PERST#     | Output | Down device PCIe Reset.                   | 3.3V  |    | 1     | Conn1   |   |

| = 22.12.1      |        | Vendor specific.                          |       |    |       |         |   |

|                |        | Host power good. Active                   |       |    |       |         |   |

|                |        | high when P48V, P12V,                     |       |    |       |         |   |

|                |        | P3V3 voltages are stable                  |       |    |       |         |   |

| HOST_PWRGD     | Input  | and within specifications.                | 3.3V  |    | 1     | Conn0   |   |

|                |        | This is considered the                    |       |    |       |         |   |

|                |        | "Power Enable" signal for                 |       |    |       |         |   |

|                |        | the module.                               |       |    |       |         |   |

|                |        | Module power good.                        |       |    |       |         |   |

|                |        | Active high when the                      |       |    |       |         |   |

| MODULE_PWRGD   | Output | module has completed its                  | 3.3V  |    | 1     | Conn0   |   |

|                |        | own power up sequence                     |       |    | _     |         |   |

|                |        | Land ic roady for DEDCT#                  | i     | Ì  | l .   |         | I |

|                |        | and is ready for PERST# de-assertion      |       |    |       |         |   |

| PWRBRK# Input reduction. CEM 3.3V 1 Conn0 Compliant Power Break Power Reduction GPIO to instruct OAM to go |  |

|------------------------------------------------------------------------------------------------------------|--|

| Compliant Power Break Power Reduction GPIO to instruct OAM to go                                           |  |

| Power Reduction GPIO to instruct OAM to go                                                                 |  |

| instruct OAM to go                                                                                         |  |

|                                                                                                            |  |

|                                                                                                            |  |

| certain stage to reduce                                                                                    |  |

| power                                                                                                      |  |

| 11 - default state LO,                                                                                     |  |

| normal power                                                                                               |  |

| 10 - L1, 1st level power                                                                                   |  |

| PWRRDT#[1:0]Inputreduction.3.3V2Conn1                                                                      |  |

| 01 - L2, 2nd level power                                                                                   |  |

| reduction.                                                                                                 |  |

| 00 - L3, max power                                                                                         |  |

| reduction.                                                                                                 |  |

| Details defined by specific                                                                                |  |

| OAM product                                                                                                |  |

| specification.                                                                                             |  |

| Catastrophic thermal                                                                                       |  |

| event for module                                                                                           |  |

| components. Active low                                                                                     |  |

| and latched by the                                                                                         |  |

| THERMTRIP# Output Module logic. Released 3.3V 1 Conn0                                                      |  |

| until motherboard power                                                                                    |  |

| cycles the module input                                                                                    |  |

| voltages                                                                                                   |  |

| Module node identifier                                                                                     |  |

|                                                                                                            |  |

| MODULE_ID[4:0] Input (e.g. Module #0, #1,#n).  Module has weak PU to 5 Conn0                               |  |

|                                                                                                            |  |

| drive to 1 by default.                                                                                     |  |

| Mezz Module Host                                                                                           |  |

| Interface/SerDes Link                                                                                      |  |

| Configuration and                                                                                          |  |

| LINK_CONFIG[4:0] Input topology. See link config 5 Conn1                                                   |  |

| table for details. The                                                                                     |  |

| module has weak PU to                                                                                      |  |

| Vref to drive high by                                                                                      |  |

| default.                                                                                                   |  |

| x16 Host Interface                                                                                         |  |

| Bifurcation Configuration.                                                                                 |  |

| 00 = one x16 PCIe host                                                                                     |  |

| interface                                                                                                  |  |

| 01 = bifurcation into two                                                                                  |  |

| PE_BIF[1:0]Outputx8 PCle host interfaces2Conn1                                                             |  |

| 10 = bifurcation into four                                                                                 |  |

| x4 PCle host interfaces                                                                                    |  |

| 11 = reserved                                                                                              |  |

| Vref based when drive to                                                                                   |  |

| high.                                                                                                      |  |

| PLINK_CAP     | Output                 | "P" Port Module Capability support: '0' = PCle only support '1' = Alternate protocol supported The host system requests an alternate host link protocol by pulling up LINK_CONFIG[0] and the Module informs the system of protocol support on the "P" link via this pin. If the module only supports PCle as host, this signal is PD on the module. | Vref | 1 | Conn1 |                   |

|---------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|-------|-------------------|

| SMBus_SLV_D   | Bi-<br>direction<br>al | Slave SMBus data.                                                                                                                                                                                                                                                                                                                                   | 3.3V | 1 | Conn0 | I3C<br>compatible |

| SMBus_SLV_CLK | Input                  | Slave SMBus clock                                                                                                                                                                                                                                                                                                                                   | 3.3V | 1 | Conn0 | I3C<br>compatible |

| SLV_ALERT#    | Output                 | Slave alert indication. 3                                                                                                                                                                                                                                                                                                                           |      | 1 | Conn0 |                   |

| 12C_D         | Bi-<br>direction<br>al | Master I2C/SMBus data .<br>PU on OAM.                                                                                                                                                                                                                                                                                                               | Vref | 1 | Conn0 | I3C<br>compatible |

| I2C _CLK      | Output                 | Master I2C/SMBus clock.<br>PU on OAM.                                                                                                                                                                                                                                                                                                               | Vref | 1 | Conn0 | I3C<br>compatible |

| UART_TXD      | Output                 | Serial Port Transmit                                                                                                                                                                                                                                                                                                                                | 3.3V | 1 | Conn0 |                   |

| UART_RXD      | Input                  | Serial Port Receive                                                                                                                                                                                                                                                                                                                                 | 3.3V | 1 | Conn0 |                   |

| JTAG0_TRST    | Input                  | Low Voltage ASIC/GPU<br>JTAG Test Reset                                                                                                                                                                                                                                                                                                             | Vref | 1 | Conn0 |                   |

| JTAG0_TMS     | Input                  | Low Voltage ASIC/GPU<br>JTAG Test Mode Select                                                                                                                                                                                                                                                                                                       | Vref | 1 | Conn0 |                   |

| JTAG0_TCK     | Input                  | Low Voltage ASIC/GPU<br>JTAG Test Clock                                                                                                                                                                                                                                                                                                             | Vref | 1 | Conn0 |                   |

| JTAG0_TDO     | Low Voltage ASIC/GDU   |                                                                                                                                                                                                                                                                                                                                                     | Vref | 1 | Conn0 |                   |

| JTAG0 _TDI            | Input  | Low Voltage ASIC/GPU<br>JTAG Test Input                                                                                                                                                    | I VIET I I |         | 1        | Conn0    |          |

|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|----------|----------|----------|

| JTAG1_TRST            | Input  | High Voltage JTAG Test<br>Reset                                                                                                                                                            | 3.3V       |         | 1        | Conn1    | optional |

| JTAG1_TMS             | Input  | High Voltage JTAG Test Mode Select                                                                                                                                                         | 3.3V       |         | 1        | Conn1    | optional |

| JTAG1_TCK             | Input  | High Voltage JTAG Test<br>Clock                                                                                                                                                            | 3.3V       |         | 1        | Conn1    | optional |

| JTAG1_TDO             | Output | High Voltage JTAG Test Output                                                                                                                                                              | 3.3V       |         | 1        | Conn1    | optional |

| JTAG1_TDI             | Input  | High Voltage JTAG Test Input                                                                                                                                                               | 3.3V       |         | 1        | Conn1    | optional |

| PRSNTO#               | Output | Module present pin connector 0. Tied to GND through 1K resistor on module side.                                                                                                            |            |         | 1 Cor    |          |          |

| PRSNT1#               | Output | Module present pin<br>connector 1. Tied to GND<br>through 1K resistor on<br>module side                                                                                                    |            |         | 1 Cor    |          |          |

| SCALE_DEBUG_EN        | Output | At-scale debug enable on<br>the module. Isolates any<br>motherboard JTAG debug<br>path when logic High                                                                                     | 3.3V       | 3.3V 1  |          | Conn0    |          |

| DEBUG_PORT_PRS<br>NT# | Input  | Presence signal for debug port in baseboard. Notifies logic in the module the debug access is being used by the baseboard debug connector. Debug port on baseboard present when logic low. | Vref       |         | 1        | Conn0    |          |

| MNGMT_LINK0Tp<br>/n   | Output | Vendor specific module<br>to module management<br>link port 0 transmit                                                                                                                     |            | 1 Conn1 |          | Conn1    | Optional |

| MNGMT_LINK0Rp<br>/n   | Input  | Vendor specific module<br>to module management<br>link port 0 receive                                                                                                                      | 1          |         | Conn1    | Optional |          |

| MNGMT_LINK1Tp<br>/n   | Output | Vendor specific module<br>to module management<br>link port 1 transmit                                                                                                                     | 1 Conn1    |         | Optional |          |          |

| MNGMT_LINK1Rp<br>/n   | Input  | Vendor specific module<br>to module management<br>link port 1 receive                                                                                                                      | 1 Conn1    |         | Conn1    | Optional |          |

| TESTO                 | 1/0    |                                                                                                                                                                                            | Vref       |         | 1        | Conn0    | Optional |

| TEST1                 | I/O    |                                                                                                                                                                                            | Vref       |         | 1        | Conn0    | Optional |

| TEST2        | I/O   |                                                                                              | Vref | 1   | Conn0 | Optional |

|--------------|-------|----------------------------------------------------------------------------------------------|------|-----|-------|----------|

| TEST3        | 1/0   |                                                                                              | Vref | 1   | Conn0 | Optional |

| TEST4        | 1/0   |                                                                                              | Vref | 1   | Conn0 | Optional |

| TEST5        | 1/0   |                                                                                              | Vref | 1   | Conn0 | Optional |

| TEST6        | 1/0   |                                                                                              | Vref | 1   | Conn0 | Optional |

| TEST7        | 1/0   |                                                                                              | Vref | 1   | Conn0 | Optional |

| TEST8        | 1/0   |                                                                                              | Vref | 1   | Conn1 | Optional |

| TEST9        | 1/0   |                                                                                              | Vref | 1   | Conn1 | Optional |

| TEST10       | 1/0   |                                                                                              | Vref | 1   | Conn1 | Optional |

| TEST11       | 1/0   |                                                                                              | Vref | 1   | Conn1 | Optional |

| TEST12       | 1/0   |                                                                                              | Vref | 1   | Conn1 | Optional |

| TEST13       | 1/0   |                                                                                              | Vref | 1   | Conn1 | Optional |

| TEST14       | 1/0   |                                                                                              | Vref | 1   | Conn1 | Optional |

| MANF_MODE#   | Input | Manufacturing Mode 1: Normal operation 0: Module enter into manufacturing mode               | 3.3V | 1   | Conn0 |          |