# Grand Canyon Storage System Specification

Revision 1.0 9/14/2022

Authors:

Abe Garcia, Hardware Engineer, Meta Chenyu Xu / Dmitriy Shapiro, Mechanical Engineer, Meta Dan Zhang, Software Engineer, OpenBMC, Meta Jeff Puglis, Hardware Engineer, Meta Madhavan Ravi, Hardware Engineer, Meta Rajesh Kasukurthy, Thermal Engineer, Meta

| Table of Contents                                                 |     |

|-------------------------------------------------------------------|-----|

| 1. LICENSE                                                        | 9   |

| 1.1. OCP CLA                                                      | 9   |

| 2. OCP TENETS COMPLIANCE                                          | 10  |

| 2.1 Openness                                                      | 10  |

| 2.2. Efficiency                                                   | 10  |

| 2.3. Impact                                                       | 10  |

| 2.4. Scale                                                        | 11  |

| 3. REVISION TABLE                                                 | 12  |

| 4. SCOPE                                                          | 13  |

| 5. OVERVIEW                                                       | 13  |

| 5.1 System Architecture                                           | 13  |

| 5.1.1 System Design and Flexibility                               | 13  |

| 5.1.2 System Improvements from Bryce Canyon                       | 15  |

| 5.2 System Components                                             | 16  |

| 5.2.1 Barton Springs (Codename for the Integrated 1S Server Card) | 16  |

| 5.2.2 Storage Controller Card                                     | 17  |

| 5.2.4 IOC Module                                                  | 19  |

| 5.2.5 E1.S SSD                                                    | 21  |

| 5.2.6 OCP3.0 NIC                                                  | 22  |

| 5.2.7 Drive Plan Board (DPB)                                      | 22  |

| 5.2.8 Power Transfer Board (PTB)                                  | 25  |

| 5.2.9 Power Cable-Track and Power Delivery Board                  | 25  |

| 5.3 System Configurations                                         | 26  |

| 5.3.1 Dual Storage Server                                         | 28  |

| 5.3.2 Single Storage Server                                       | 28  |

| 5.3.3 JBOD                                                        | 29  |

| 5.4 Systems Management Overview                                   | 30  |

| 6. RACK COMPATIBILITY                                             | 33  |

| 7. RACK IMPLEMENTATION                                            | 33  |

| 7.1 Type 5                                                        | 176 |

| 7.2 Type 7                                                        | 34  |

| 7.3 Compatibility with Open Rack Standard                         | 35  |

| 8. SYSTEM INTERACTION AND SERVICEABILITY                            | 35 |

|---------------------------------------------------------------------|----|

| 8.1 Labeling of Logical Domains                                     | 35 |

| 8.2 LEDs and Buttons                                                | 38 |

| 8.2.1 Front Panel Buttons and LEDs                                  | 38 |

| 8.2.1.1 Power Button                                                | 39 |

| 8.2.1.2 Power LED                                                   | 39 |

| 8.2.1.3 Reset Button                                                | 39 |

| 8.2.1.5 USB Debug Port                                              | 40 |

| 8.2.1.6 SSD LEDs                                                    | 40 |

| 8.2.1.7 NIC LEDs                                                    | 41 |

| 8.2.1.8 IOC Module LEDs                                             | 41 |

| 8.2.3 HDD LED behaviors                                             | 41 |

| 8.2.4 Fan Module LEDs                                               | 42 |

| 8.3 Hard Drive Serial Number Window                                 | 42 |

| 8.4 Service Operations                                              | 43 |

| 8.4.1 HDD Replacement                                               | 43 |

| 8.4.2 SSD Replacement                                               | 44 |

| 8.4.3 SCC Replacement                                               | 45 |

| 8.4.4 UIC Replacement                                               | 46 |

| 8.4.5 UIC TPM & BSM Replacement                                     | 47 |

| 8.4.6 NIC Replacement                                               | 48 |

| 8.4.7 Barton Springs Replacement                                    | 49 |

| 8.4.8 IOC Module Replacement                                        | 50 |

| 8.4.9 Fan Module Replacement                                        | 51 |

| 8.4.10 Fan Louver & Honeycomb Replacement                           | 52 |

| 8.4.11 Drive Plan Board Replacement                                 | 54 |

| 8.4.12 Cable Track and Power Delivery Board Replacement             | 56 |

| 9. SYSTEM PERFORMANCE                                               | 58 |

| 9.1 Designing the system interfaces without bottlenecks             | 58 |

| 9.2 HDD performance degradation due to vibrations                   | 59 |

| 9.2.1 Normal Operating Environment (sustained operating conditions) | 60 |

| 9.2.2 Unsustained Operating Conditions                              | 60 |

| 9.2.3 Design Criteria to Enable Chassis Longevity                   | 60 |

| 10. ELECTRICAL DESIGN                                               | 60 |

| 10.1 PCIe Topology                                                  | 60 |

| 10.1.1 PCIe Mapping                                                 | 60 |

| 10.1.2 PCIe Clocks and Resets                                       | 62 |

|                                                                     |    |

| 10.2 System Management                                            | 64 |

|-------------------------------------------------------------------|----|

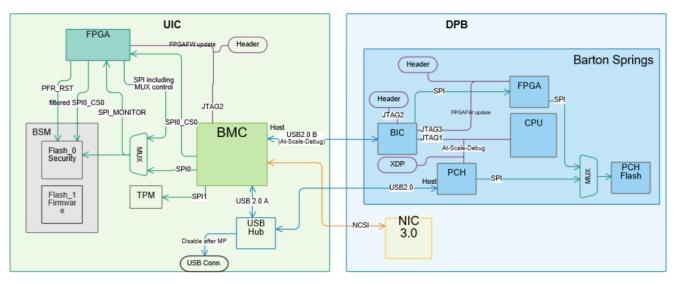

| 10.2.1 Device Management signaling                                | 64 |

| 10.2.2 I2C Topology                                               | 65 |

| 10.2.3 USB, SPI, JTAG                                             | 67 |

| 10.2.4 Network Controller Sideband Interface (NC-SI) requirements | 68 |

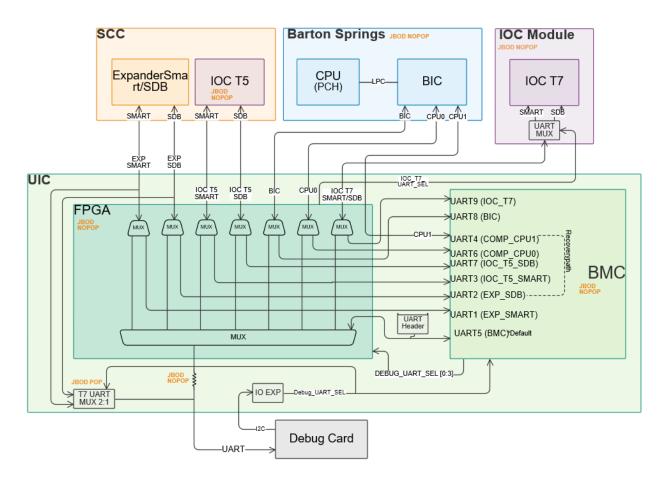

| 10.2.5 UART                                                       | 68 |

| 10.2.6 GPIO (Insert) Topology                                     | 69 |

| 10.2.8 Fan control                                                | 70 |

| 10.2.9 System Configurations                                      | 72 |

| 10.2.9.1 Integrated (Dual) Configuration                          | 72 |

| 10.2.9.2 Integrated (Single) Configuration                        | 72 |

| 10.2.9.3 JBOD Configuration                                       | 73 |

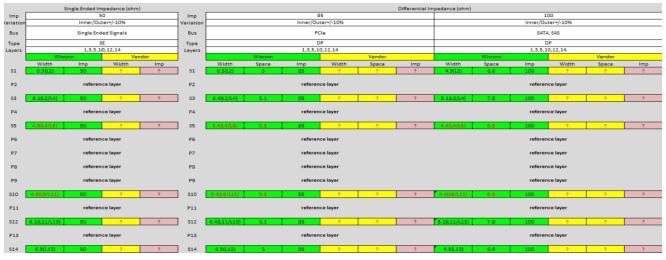

| 10.3 Signal Integrity requirements                                | 73 |

| 10.3.1 SAS/SATA                                                   | 73 |

| 10.3.2 PCIe                                                       | 73 |

| 10.4 ESD Compliance                                               | 73 |

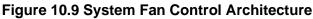

| 11. POWER                                                         | 73 |

| 11.1 Power Topology                                               | 73 |

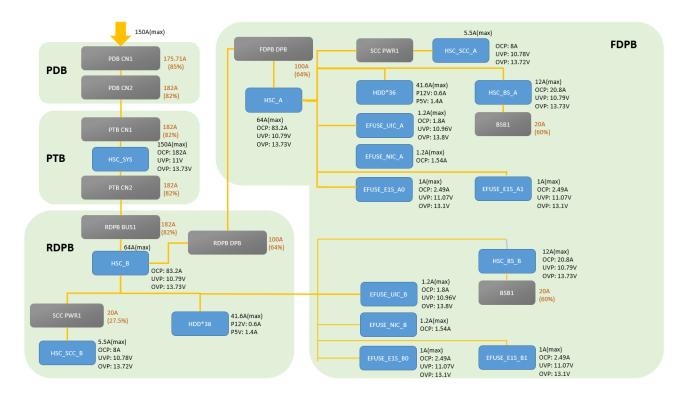

| 11.2 System Grounding Topology                                    | 73 |

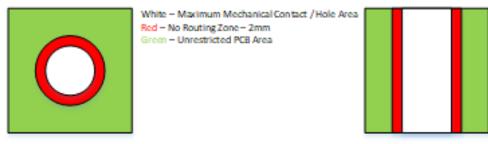

| 11.2.1 Mechanical Interface Isolation Distance                    | 75 |

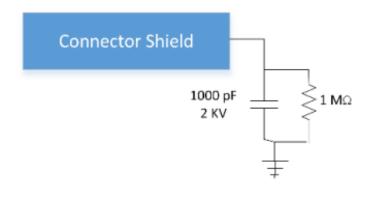

| 11.2.2 Connector Housing Ground Topology                          | 76 |

| 11.3 12V Busbar Cable Input                                       | 76 |

| 11.4 Drive Power Requirements                                     | 77 |

| 11.4.1 Staggered spin up requirements                             | 77 |

| 11.4.2 Hot-Swap Requirements                                      | 77 |

| 11.4.3 5V Conversion Failure Domains                              | 77 |

| 11.4.4 5V Conversion Loading Requirements                         | 78 |

| 11.5 Hot-Swap Requirements                                        | 78 |

| 11.5.1 Capacitive Load                                            | 78 |

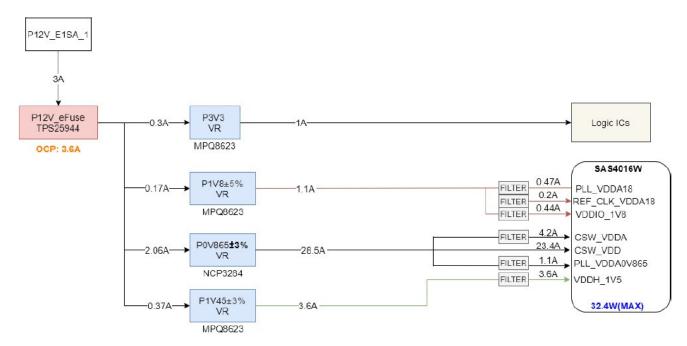

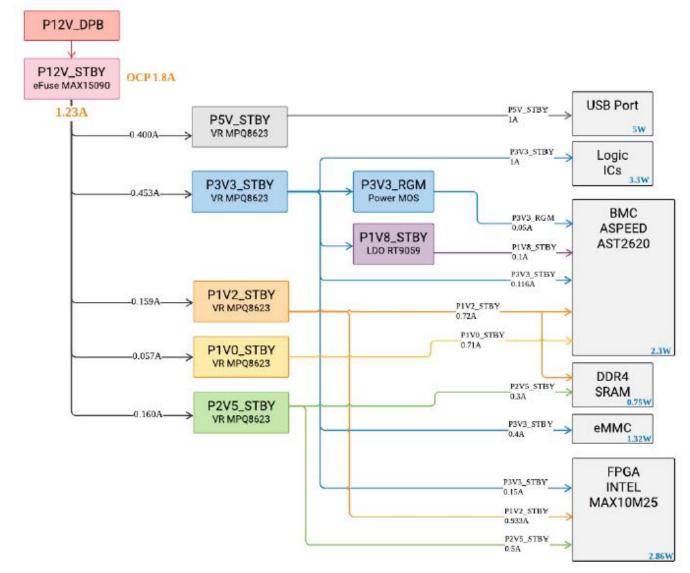

| 11.6 IOCM Power Topology                                          | 78 |

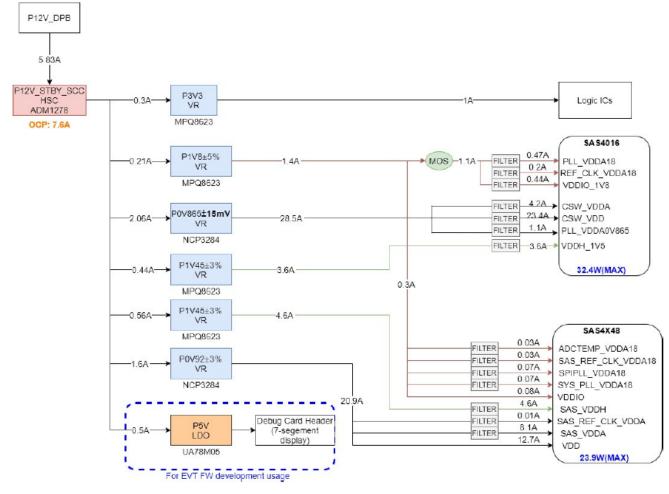

| 11.7 Storage Controller Card Power Topology                       | 80 |

| 11.8 User Interface Card Power Topology                           | 81 |

| 11.9 Power Budget                                                 | 81 |

| 11.9.1 System Power Budget                                        | 81 |

| 11.9.2 SCC Connector Power Budget                                 | 82 |

| 11.9.3 IOCM Connector Power Budget                                | 82 |

| 11.9.4 UIC Connector Power Budget                                 | 82 |

|                                                                   |    |

| 11.10 Power Sequencing                               | 82  |

|------------------------------------------------------|-----|

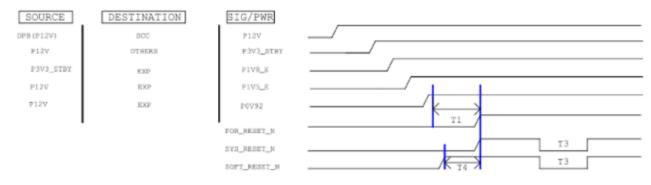

| 11.10.1 SCC Power Sequencing                         | 82  |

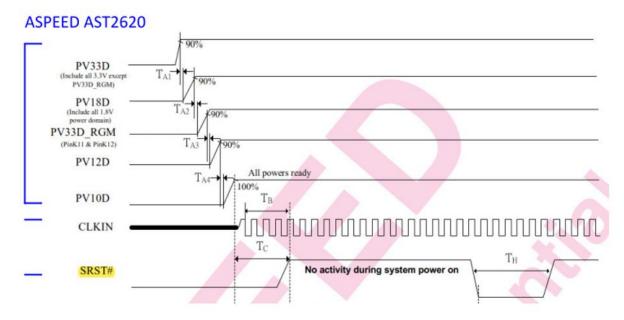

| 11.10.2 Barton Springs Power Sequencing              | 83  |

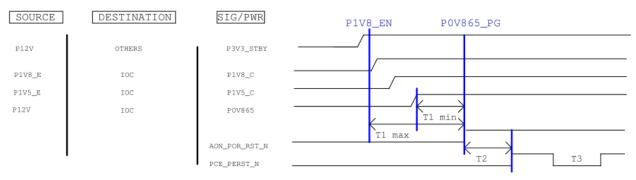

| 11.10.3 IOCM Power Sequencing                        | 83  |

| 11.10.4 UIC Power Sequencing                         | 84  |

| 12 INDIVIDUAL PCBA SPECIFICATIONS                    | 85  |

| 12.1 Drive Plane Boards (RDPB & FDPB)                | 85  |

| 12.1.1 Connectors                                    | 85  |

| 12.1.1.1 Compute Slots                               | 176 |

| 12.1.1.2 SCC Connectors                              | 176 |

| 12.1.1.3 E1.S/IOCM Connectors                        | 85  |

| 12.1.1.4 NIC Connectors                              | 85  |

| 12.1.1.5 UIC Connectors                              | 85  |

| 12.1.1.6 HDD Connectors                              | 176 |

| 12.1.1.7 12V System Power Input                      | 86  |

| 12.1.1.8 DPB to DPB Power Connectors                 | 86  |

| 12.1.1.9 DPB to DPB Signal Connectors                | 86  |

| 12.1.1.10 Fan Connectors                             | 86  |

| 12.1.2 LEDs                                          | 86  |

| 12.1.2.1 Drive Activity                              | 86  |

| 12.1.2.2 Drive Fault/Identification                  | 86  |

| 12.1.3 Thermal Sensor Placement                      | 86  |

| 12.1.4 I2C Component Placement                       | 87  |

| 12.1.5 Drawer Detection Sensor                       | 87  |

| 12.1.6 Drive Control Signals                         | 87  |

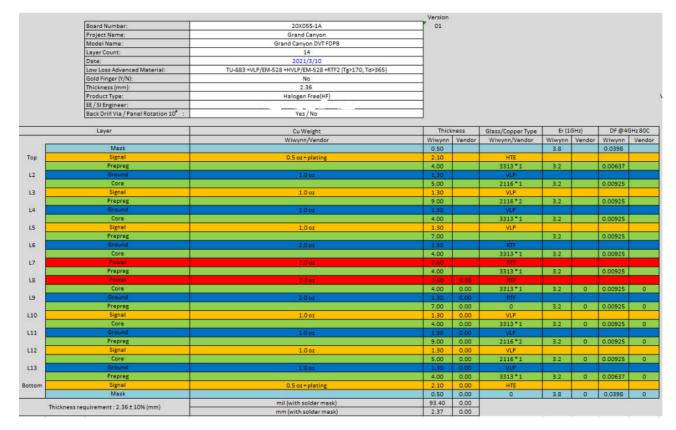

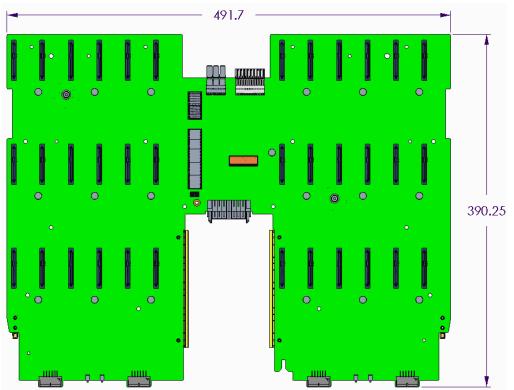

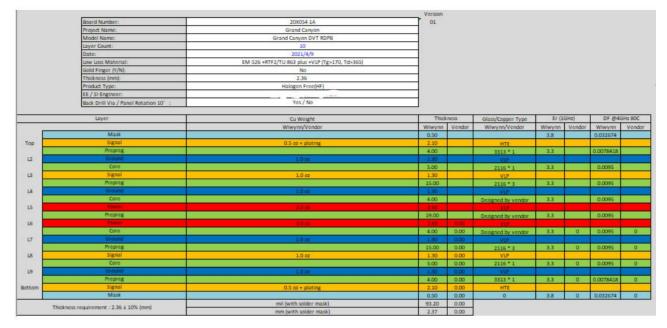

| 12.1.7 PCB Details                                   | 88  |

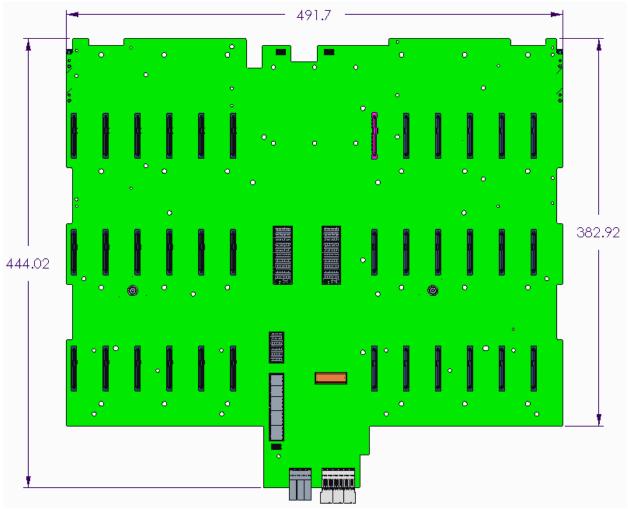

| 12.1.7.1 Front DPB                                   | 88  |

| 12.1.7.1.1 Important Components and Features         | 88  |

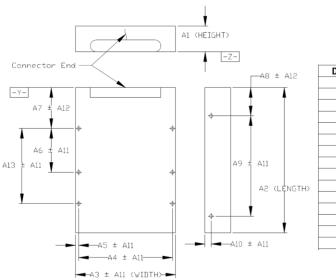

| 12.1.7.1.2 PCB Key Dimensions                        | 89  |

| 12.1.7.2 Rear DPB                                    | 91  |

| 12.1.7.2.1 Important Component and Features          | 91  |

| 12.1.7.2.2 PCB Key Dimensions                        | 92  |

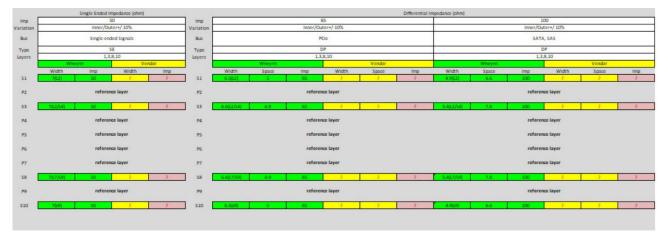

| 12.1.7.2.3 PCB Stackup                               | 93  |

| 12.2 Storage Controller Card (SCC)                   | 93  |

| 12.2.1 Storage Controller Card Configuration Diagram | 94  |

| 12.2.2 Storage Controller Card Configurations        | 176 |

| 12.2.2.1 Connector Configurations                    | 176 |

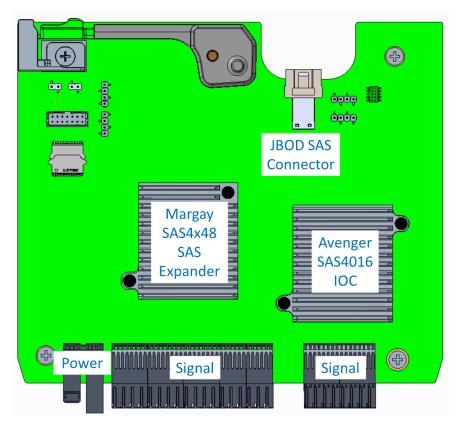

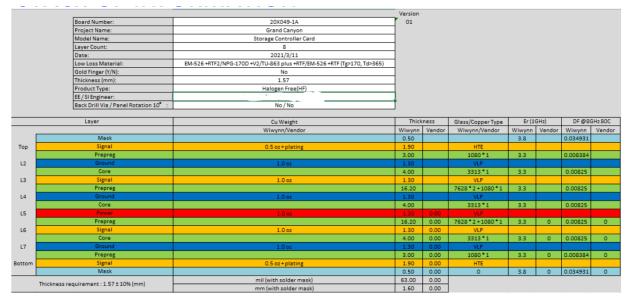

| 12.2.5 Storage Controller Card PCB           | 95  |

|----------------------------------------------|-----|

| 12.2.5.1 Important Components and interfaces | 95  |

| 12.2.5.2 PCB Key Dimensions                  | 97  |

| 12.2.5.3 PCB Stack up                        | 97  |

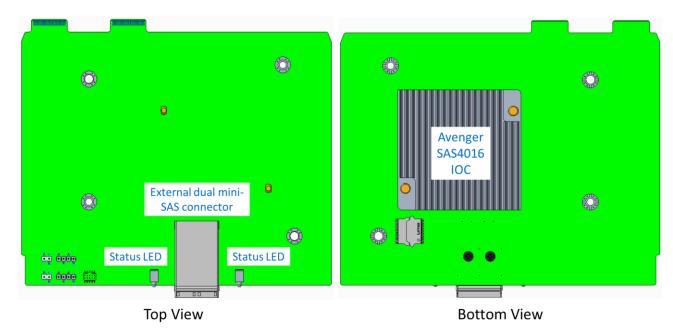

| 12.3 IOCM                                    | 98  |

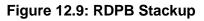

| 12.3.1 IOCM Configuration Diagram            | 98  |

| 12.3.2 IOCM Connectors                       | 176 |

| 12.3.3 IOCM Card PCB                         | 176 |

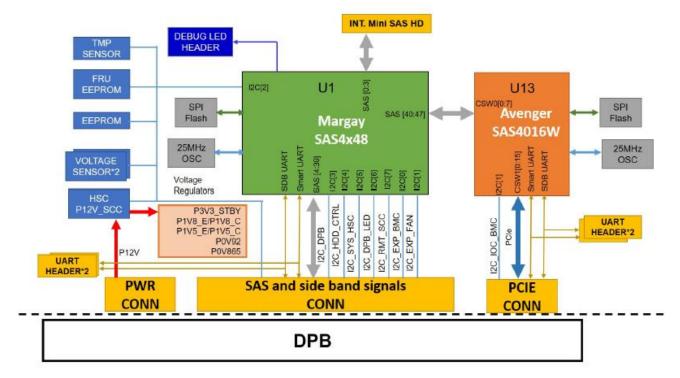

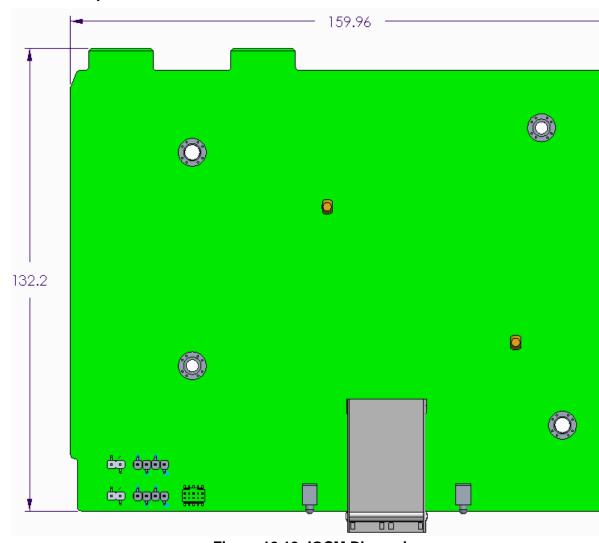

| 12.3.3.1 Important Components and Interfaces | 100 |

| 12.3.3.2 PCB Key Dimensions                  | 101 |

| 12.3.3.3PCB Stackup                          | 102 |

| 12.4 User Interface Card (UIC)               | 102 |

| 12.4.1 UIC Variants                          | 102 |

| 12.4.2 BMC                                   | 176 |

| 12.4.3 CPLD                                  | 176 |

| 12.4.4 Connectors                            | 104 |

| 12.4.5 USB Debug                             | 105 |

| 12.4.6 BSM and TPM 2.0                       | 105 |

| 12.4.7 User Interface Card PCB               | 106 |

| 12.4.7.1 PCB Key Dimensions                  | 106 |

| 12.4.7.2 PCB Stack up                        | 106 |

| 12.5 Power Delivery Board (PDB)              | 107 |

| 12.5.1 Configuration Diagram                 | 107 |

| 12.5.2 Connectors                            | 176 |

| 12.5.3 PDB PCB                               | 176 |

| 12.5.3.1 Important Components and Interfaces | 108 |

| 12.5.3.2 PCB Key Dimensions                  | 109 |

| 12.5.3.3 PCB Stack up                        | 109 |

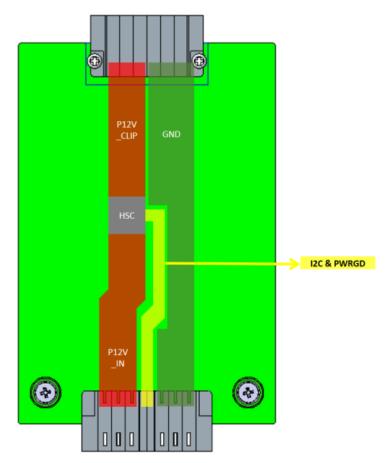

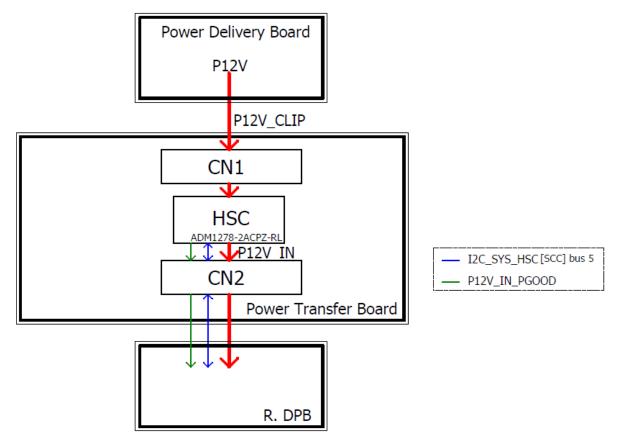

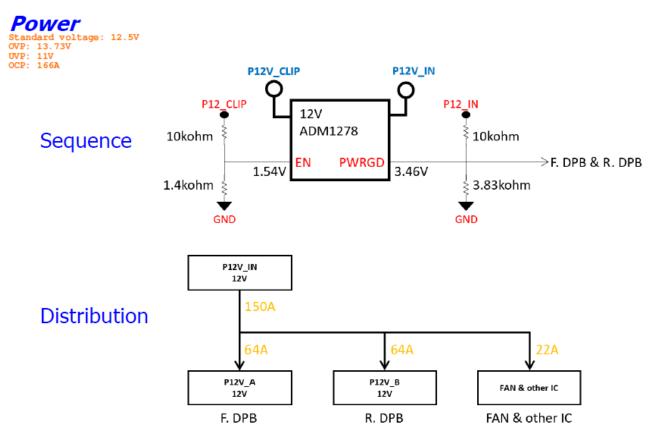

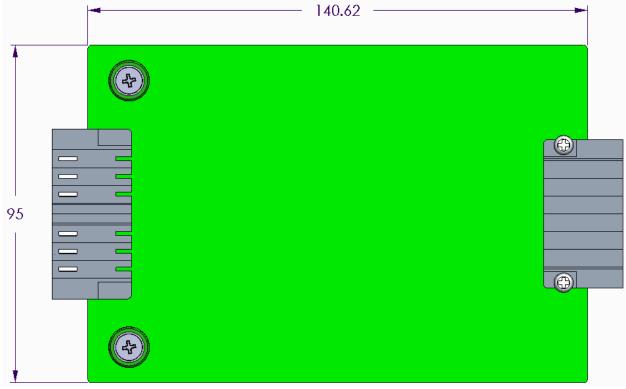

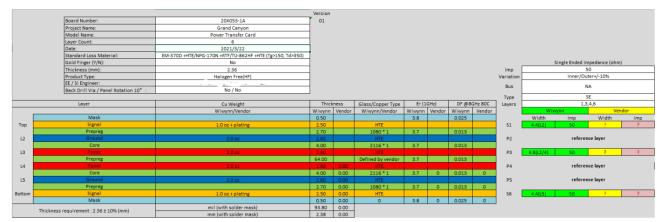

| 12.6 Power Transfer Board (PTB)              | 110 |

| 12.6.1 Configuration Diagram                 | 110 |

| 12.6.2 Connectors                            | 176 |

| 12.6.3 PTB PCB                               | 111 |

| 12.6.3.1 Important Components and Interfaces | 111 |

| 12.6.3.2 PCB Key Dimensions                  | 113 |

| 12.6.3.3 PCB Stack up                        | 113 |

| 13. INTERNAL CABLES                          | 114 |

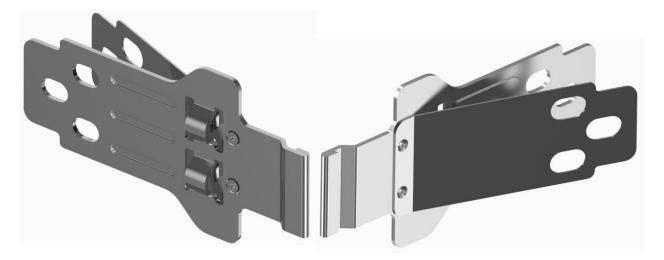

| 13.1 JBOD Connection Bracket                 | 114 |

| 13.2 Single Server SAS Cable                  | 115 |

|-----------------------------------------------|-----|

| 14. EXTERNAL CABLES                           | 115 |

| 14.1 JBOD configuration                       | 115 |

| 14.2 Cable Details                            | 116 |

| 15 BMC OVERVIEW                               | 117 |

| 15.1 Introduction                             | 117 |

| 15.2 Front Panel                              | 117 |

| 15.2.1 OCP Debug Card                         | 117 |

| 15.3 Power Control                            | 117 |

| 15.4 Remote Console                           | 120 |

| 15.5 IPMI FRUID                               | 120 |

| 15.6 Sensor Information                       | 121 |

| 15.7 Firmware Information/Update              | 121 |

| 15.8 Log Information                          | 122 |

| 15.9 Fan Speed Control                        | 122 |

| 15.10 Enclosure Management                    | 122 |

| 15.10.1 HDDs Status                           | 122 |

| 15.10.2 Error Code                            | 122 |

| 15.11 Event List Along With The Error Code    | 128 |

| 15.12 IPMI Command Support List               | 132 |

| 15.13 Expander IPMB Command Support List      | 145 |

| 16. EXPANDER FIRMWARE OVERVIEW                | 151 |

| 16.1 Drive LEDs                               | 151 |

| 16.1.1 Drive Link LED                         | 151 |

| 16.1.2 Drive Fault / Identification LED       | 152 |

| 16.1.3 Drawer Open Thermal Warning Behavior   | 152 |

| 16.2 Power Readings                           | 153 |

| 16.3 Runtime System Configurations            | 153 |

| 16.4 Report Status of GPIOs                   | 154 |

| 16.5 Even Report and Log                      | 154 |

| 16.6 Security Features                        | 154 |

| 17. THERMAL DESIGN SPECIFICATION/REQUIREMENTS | 154 |

| 17.1. Data Center Environmental Conditions    | 155 |

| 17.1.1 Location of Data Center/Altitude       | 155 |

| 17.1.2 Cold-Aisle Temperature                 | 155 |

| 17.1.3 Cold-Aisle Pressurization              | 155 |

| 17.1.4 Relative Humidity                      | 155 |

|-----------------------------------------------|-----|

| 17.2 System Thermal Operational Conditions    | 155 |

| 17.2.1 Inlet Temperature                      | 155 |

| 17.2.2 Pressurization                         | 155 |

| 17.2.3 Fan Redundancy                         | 156 |

| 17.2.4 Service Mode                           | 156 |

| 17.2.5 Delta T                                | 156 |

| 17.2.6 System Airflow or Volumetric Flow      | 156 |

| 17.2.7 Thermal Margin                         | 156 |

| 17.2.8 Thermal Sensor                         | 156 |

| 17.3 Grand Canyon Thermal Design Requirements | 176 |

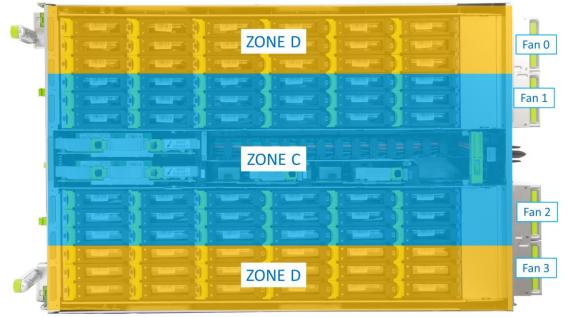

| 17.3.1 Fans                                   | 157 |

| 17.3.2 Cooling Zones                          | 157 |

| 17.3.3 92mm Fan Module                        | 157 |

| 17.3.4 Air Baffles                            | 159 |

| 18. MECHANICAL                                | 162 |

| 18.1. Overview                                | 162 |

| 18.2. Overall Dimensions                      | 176 |

| 18.3. Rotational Vibration Requirements       | 176 |

| 18.4 Drive Plane Board                        | 176 |

| 18.5 Drawer Structural Walls                  | 164 |

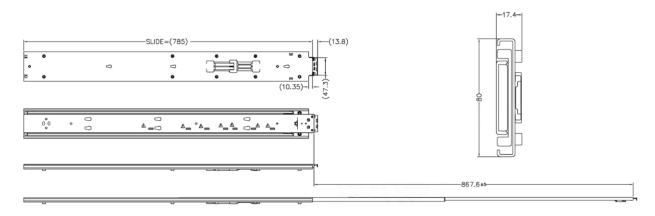

| 18.6 Slide Rail                               | 176 |

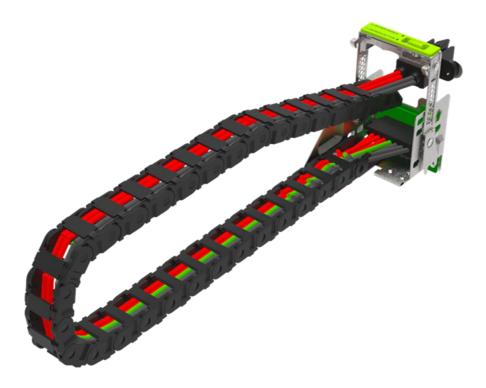

| 18.7 Bus Bar Power Module & Cable Track       | 176 |

| 18.8. Drawer Release Handles                  | 176 |

| 18.9. Rack Release Latching                   | 176 |

| 18.10 Chassis Lift Handles                    | 168 |

| 18.11 Drive Retention                         | 169 |

| 18.12 UIC and IOC Module                      | 171 |

| 18.13 Storage Controller Card                 | 171 |

| 19. ENVIRONMENTAL AND REGULATIONS             | 172 |

| 19.1 Regulatory Compliance                    | 172 |

| 19.2 Product Safety Compliance                | 172 |

| 20. ENVIRONMENTAL REQUIREMENTS                | 173 |

| 20.1. Vibration & Shock                       | 176 |

| 20.2 Regulations                              | 176 |

| 20.3 Chassis Labels and Markings              | 176 |

|                                               |     |

| 20.4 Data Center Design Requirements                         | 174                    |

|--------------------------------------------------------------|------------------------|

| 20.5 Mean Time Between Failure (MTBF) Requirements           | 175                    |

| 15.5.1 MTBF Prediction                                       | 175                    |

| 20.5.2 MTBF Demonstration Test                               | 175                    |

| 20.5 Certifications                                          | 175                    |

| 21. PRESCRIBED MATERIALS                                     | 175                    |

| 21.1 Disallowed Components                                   | 176                    |

| 21.2 Capacitors & Inductors                                  | 176                    |

| 21.3 Component Derating                                      | 176                    |

| 21.4 Sustainable Materials                                   | 176                    |

| 22. SYSTEM FIRMWARE                                          | 177                    |

| 23. HARDWARE MANAGEMENT                                      | 177                    |

| 23.1 Redfish Compliance                                      | 177                    |

| 23.2 Source Availability                                     | 177                    |

| 24. SECURITY                                                 | 178                    |

| 25. REFERENCES (OPTIONAL)                                    | 178                    |

| APPENDIX A - REQUIREMENTS FOR IC APPROVAL (to be completed C | ontributor of Baseline |

APPENDIX A - REQUIREMENTS FOR IC APPROVAL (to be completed Contributor of Baselin Spec)

# 1. LICENSE

## 1.1. OCP CLA

Contributions to this Specification are made under the terms and conditions set forth in **Open Compute Project Contribution License Agreement ("OCP CLA")** ("Contribution License") by: **Meta, Inc.**

You can review the signed copies of the applicable Contributor License(s) for this Specification on the OCP website at https://www.opencompute.org/legal-documents.

Usage of this Specification is governed by the terms and conditions set forth in Open Compute Project Hardware License – Permissive ("OCPHL Permissive") also known as a "Specification License".

178

**NOTE**: The following clarifications, which distinguish technology licensed in the Contribution License and/or Specification License from those technologies merely referenced (but not licensed), were accepted by the Incubation Committee of the OCP: None.

NOTWITHSTANDING THE FOREGOING LICENSES, THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT. FITNESS FOR A PARTICULAR PURPOSE. OR TITLE. RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN, THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO. OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION, INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 2. OCP TENETS COMPLIANCE

## 2.1 Openness

Grand Canyon system is open to enable large scale deployments in hyperscale type of environments leveraging OpenBMC, OCP NIC, industry standard interfaces and a modular form factor design concept. It provides flexible and open interfaces for future expandability.

## 2.2. Efficiency

Grand Canyon offers efficiency gains across the thermal management system due to mechanical improvements, performance efficiency gains due to increases in performance/watt as well as performance/TB, improved vibration mitigation to allow interoperability with future HDD capacities.

## 2.3. Impact

The Grand Canyon platform demonstrates flexibility of configurations and modularity of design. It

improves performance/watt, performance/TB, provides improved vibration for reliability while being serviceable at scale. It should be noted that the HDD slot vibration mitigation techniques enable the system to be leveraged in the future for multiple HDD generations.

## 2.4. Scale

Grand Canyon enables serviceability gains as all major system components are serviceable to be maintained at scale. It is designed such that CPU Board (Barton Springs) can be easily upgraded to the next generation of CPUs.

# 3. REVISION TABLE

| Date      | Revision | Author      | Description           |

|-----------|----------|-------------|-----------------------|

| 9/14/2022 | 1.0      | Jeff Puglis | Ready for OCP release |

|           |          |             |                       |

|           |          |             |                       |

|           |          |             |                       |

|           |          |             |                       |

|           |          |             |                       |

|           |          |             |                       |

# 4. SCOPE

This document defines the technical specifications for the Grand Canyon Storage System, hereinafter referred to as "Grand Canyon," used in the Open Compute Project.

Grand Canyon is Meta's latest HDD storage server chassis as a follow-on to the previous generation storage platform, Bryce Canyon. The Grand Canyon design retains the high level system architecture from Bryce Canyon - 4OU tall, single drawer dense storage chassis that contains up to 72 3.5" hard disk drives (HDDs), 2 compute modules, 1 NIC and 2 SSDs per compute module. This design will have an upgraded 1S Server card, UIC, Storage controller card and is Open Rack v2 (ORv2) compliant.

# 5. OVERVIEW

Grand Canyon is a refresh to the previous generation, Bryce Canyon. There were 4 major reasons that gave motivation to the need for the Grand Canyon project.

- 1. The need to address the shrinking runway for component and commodity end-of-life on Bryce Canyon and to enable continued HDD efficiency at Meta.

- Improve the System Performance headroom (compute, memory bandwidth, interface bandwidths, etc) to ensure the HDD storage server SKU can push drives to their limits and allow introduction of software features that consume system resources but enable efficient use of drives.

- Improve the HDD vibration damping features (both structural and acoustic) in the chassis via add-on options to allow for dense HDD capacity adoption in the chassis (driven by recent projections from HDD vendors using energy-assisted recording technology).

- 4. Introducing the 9.5mm heat sink E1.S form factor SSD

#### 5.1 System Architecture

#### 5.1.1 System Design and Flexibility

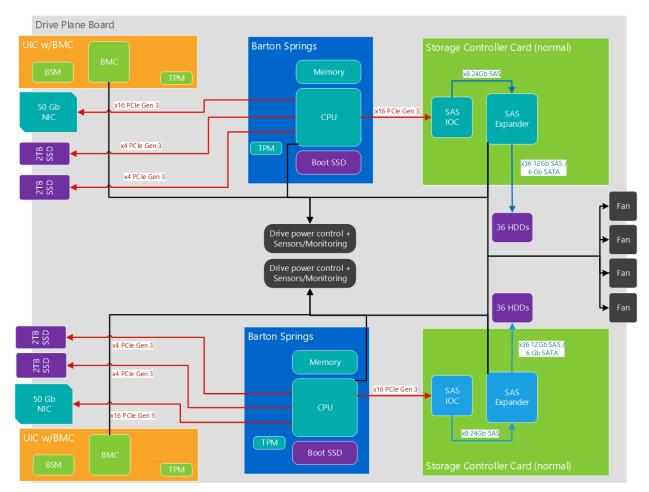

The architectural intent behind the Grand Canyon design is a flexible HDD-Storage hardware platform that enables multiple configurations for Meta's needs. From a high-level architecture perspective, Grand Canyon will be an upgrade to Bryce Canyon while retaining a lot of similarities.

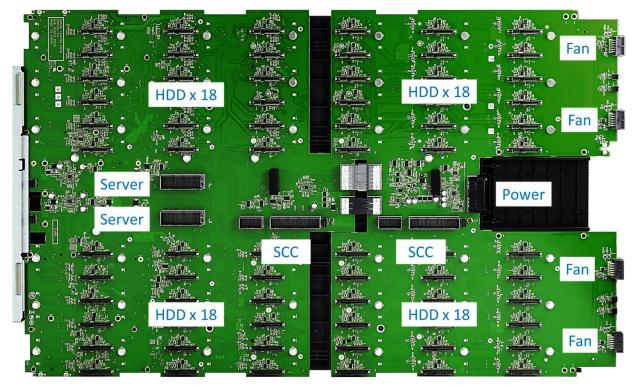

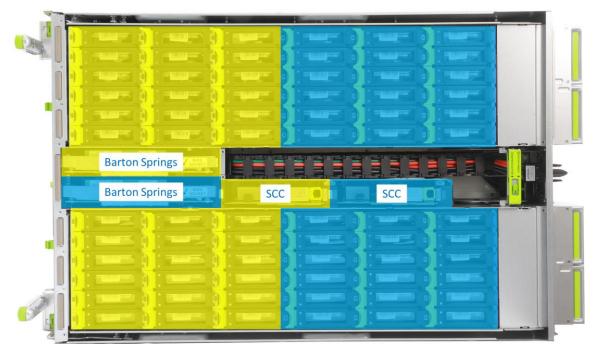

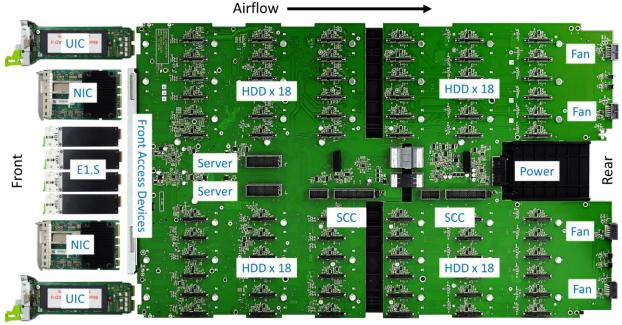

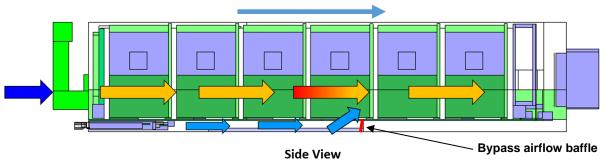

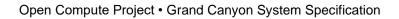

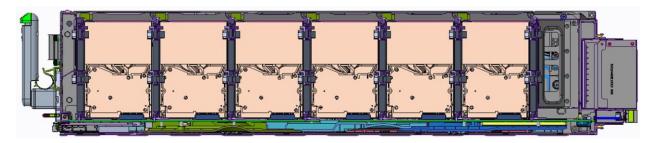

The Grand Canyon storage system is a 4OU system, with a majority of the components installed and serviced from the top. To enable this, there is an inner drawer design that fully extends the unit out of the rack, while it is still operational. A mechanical overview is shown in Figure 5.1

Multiple configurations of the chassis exist to satisfy various applications. The architecture is designed to maximize common components between configurations and modularize the components that differ. The configurations supported in Grand Canyon are dual storage server, single storage server and

JBOD. In its dual storage server configuration, the chassis supports up to 72 drives and two compute modules. Each compute module connects to a Storage Controller Card (SCC) that controls 36 drives and is logically separate from the other compute module and the 36 drives it controls.

The only common component shared by these two compute-storage groups is the Drive Plane Board assembly (like a backplane) and incoming power (12V) delivered by the bus bar clip. Grand Canyon will also design in an OCP3.0NIC (SFF) and 2x E1.S SSDs per compute node in the chassis. The chassis is designed such that the highest failure rate components (HDDs, SSDs, NICs, server card, other PCBAs) are hot-swappable without affecting the other host that resides in the same enclosure.

Figure 5.1: System Overview

#### 5.1.2 System Improvements from Bryce Canyon

|                     | CONSIDERATION                                                                                       | DETAILS                                                                                                                                                                                                                                                                         |

|---------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage<br>Solution | Implement front-serviceable data<br>SSD with provision to hotswap i.e.,<br>without system power off | Pivot to front loadable E1.S form factor<br>Hot-swappable data SSD improves system availability                                                                                                                                                                                 |

|                     | Designing with HDDs and SSDs as<br>the server's IO bottlenecks for all use<br>cases                 | Grand Canyon will start off with 50Gbps NIC and provide an upgradability option to use 100Gbps NIC, if needed                                                                                                                                                                   |

|                     | Designing for Dual actuator adoption                                                                | Power delivery, thermal and vibration control will be designed into the chassis to support Dual actuator adoption.                                                                                                                                                              |

|                     |                                                                                                     | CPU server card and NIC upgrades to support dual-actuator drives will be drop-in replacements                                                                                                                                                                                   |

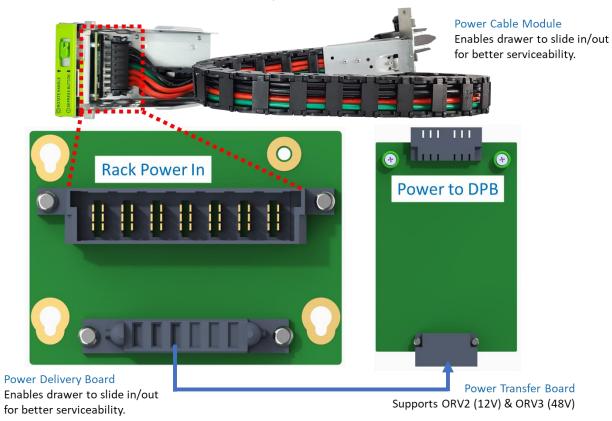

| DC<br>Operations    | Power cable track redesign to improve serviceability and reliability                                | Addition of a new power delivery board in the mid-section to keep the power cable constrained in the mid-section entirely                                                                                                                                                       |

|                     | Better serviceability of the Drive<br>Plane Board                                                   | Designed for slide-out and slide-in replacement of the Drive Plane Board (DPB)                                                                                                                                                                                                  |

|                     | Design for both ORv2 and ORv3 rack configurations                                                   | <ul> <li>Design flexibility to ensure Grand Canyon can MP with Orv2 rack configuration but have the flexibility to be upgraded to Orv3 in future.</li> <li>Power delivery flexibility to move from 12V to 48V busbar</li> <li>Mechanical flexibility to move to Orv3</li> </ul> |

| Components          | CPU                                                                                                 | Intel Cooperlake 26 core - TDP =91W (including PCH)                                                                                                                                                                                                                             |

|                     | DIMM configuration                                                                                  | Dual Storage server (T5) – 4x16GB DDR4<br>Single Storage server (T7) – 4x32GB DDR4                                                                                                                                                                                              |

|                     | Boot SSD                                                                                            | m.2 2280 NVMe SSD                                                                                                                                                                                                                                                               |

|                     | Data SSD configuration                                                                              | 2x 2TB E1.S SSD per compute node inside Grand Canyon i.e., total of 4x 2TB E1.S SSDs per Grand Canyon chassis                                                                                                                                                                   |

|                     | IOC                                                                                                 | Broadcom Avenger - SAS4016W                                                                                                                                                                                                                                                     |

|                     | Expander                                                                                            | Broadcom Margay - SAS4x48                                                                                                                                                                                                                                                       |

### Table 5.1: System Improvements

|           | BMC                                                                                                | Aspeed AST2620                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | NIC                                                                                                | OCP3.0 single host multi-sourced NICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | Fans                                                                                               | Separate cages per Grand Canyon chassis<br>Rack Type 5 – 1 dual-rotor fan per cage<br>Rack Type 7 – 1 single-rotor fan per cage<br>Integrate FRU eeprom inside fans for traceability and I2C<br>system interconnect to Fans                                                                                                                                                                                                                                                                                                                                                                                         |

| Vibration | Improving vibration dampening from<br>structural and acoustic vibration<br>sources in the chassis. | <ul> <li>The chassis shall design in the following options:</li> <li>1. Fan cage isolation from chassis via elastomer padding, fan grommets</li> <li>2. Enable acoustic foam installation at strategic locations</li> <li>3. DPB air gap seal to reduce air leakage and bring max fan PWM lower than 100%.</li> <li>4. Lower fan blade count and better geometries</li> <li>5. New material on HDD latches, if needed</li> <li>6. Options to mount fan louvers to reduce air leakage on fan-failure and lower fan speeds to be less than 100%</li> <li>7. Retain wireframe fingerguard from Bryce Canyon</li> </ul> |

#### **5.2 System Components**

This section outlines the major PCBAs and FRU-able commodities that make up the system, other than the HDDs.

#### 5.2.1 Barton Springs (Codename for the Integrated 1S Server Card)

Barton Springs is the integrated 1S server card. It is a top-accessible PCBA once the drawer is pulled out of the chassis tub. As Compute workload and needs for DRAM bandwidth, connected SSD, special instructions on the CPU, etc varies quite a bit from Storage, advantages are achievable only when the Compute card designs are flexible and agile enough to adapt to evolving needs. In order to reduce the churn on a Storage chassis design tied to a server card form-factor that cannot be predicted to be constant, Grand Canyon breaks away from reusing an existing design and will standardize on a new form-factor defined by the maximum remaining volume in the chassis while accommodating 72 HDDs.

Barton Springs shall be designed to this form-factor specifically for Grand Canyon chassis to ensure we can achieve dense HDD packing within the chassis for greater advantages, make the server card form-factor modular and long-lasting to allow for CPU upgrades on the same chassis. Shown below in Figure

5.2 is a rendering of Barton Springs card with the CPU w/heatsink, PCH w/heatsink, a client m.2 SSD for boot purposes, and 4 DIMM sockets (1 DIMM per channel).

Figure 5.2: Barton Springs PCBA

The design details of the server card will be covered under the Barton Springs 1S server card design specification document.

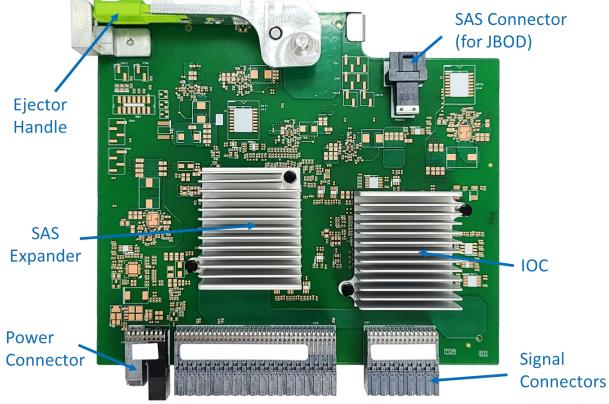

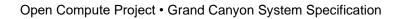

#### 5.2.2 Storage Controller Card

The Storage Controller Card (SCC) is a top-accessible module (with the drawer extended) that contains the ICs required to translate PCIe connectivity from the Server card to SAS/SATA for the HDDs. The SCC supports:

- SAS IOC, a.k.a., HBA

- SAS Expander

- SAS connections to the front bulkhead (to enable JBOD [Just a Bunch Of Disks] functionality)

The SCC connects to Barton Springs via a PCIe Gen3 x16 link. There are 2 configurations of the SCC, normal (IOC+Expander populated) and JBOD (only Expander is populated).

Figure 5.3: Storage Controller Card (SCC)

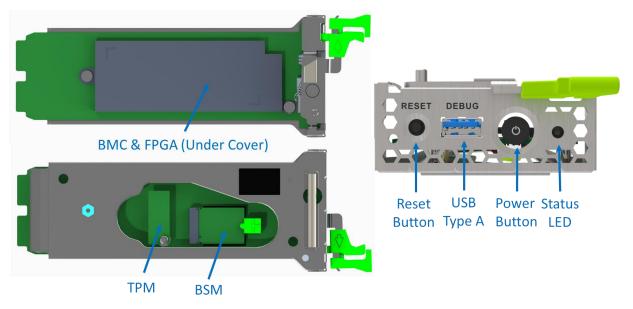

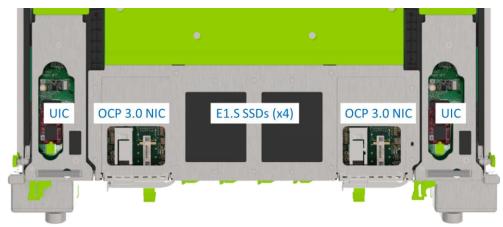

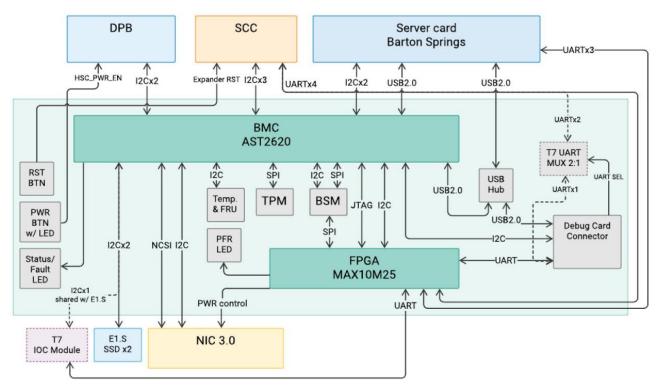

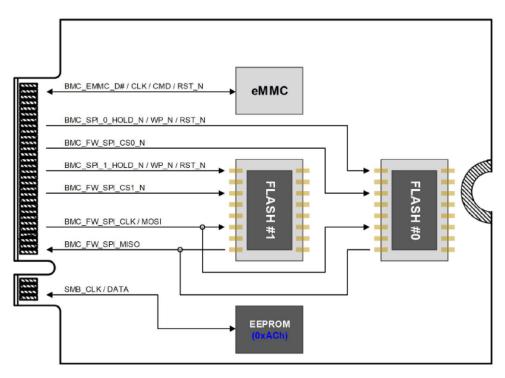

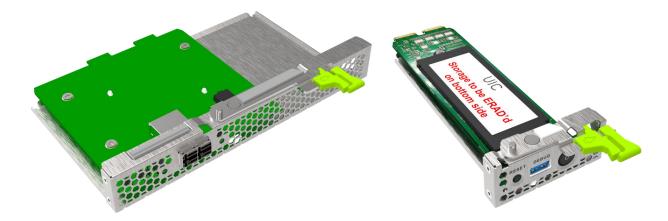

The User Interface Card is a low speed management card that houses the BMC SoC, Trusted platform Module (TPM), and a removable BMC Storage module or BSM in an m.2 2230 form factor. Since the E.1S SSD and OCP3.0 NICs are front pluggable form factors, we envision these to plug into the Front drive plane board directly and the need for an IO module card (used in Bryce Canyon) now reduces to that of the UIC.

In addition to these components, the UIC also brings out on its front panel, a debug USB Type-A connector, a bicolor status LED and a mechanical power button for one half or one node of the chassis.

- The debug USB-A connector should multiplex the UART from the BMC, Expander and host and toggle between them using the UART-SEL button on the OCP debug card.

- The bicolor status LED should indicate good health or fault status from BMC, host, and expander.

- The mechanical power button controls the enable of the Hot swap controller (HSC) that enables power for each logical half of the chassis.

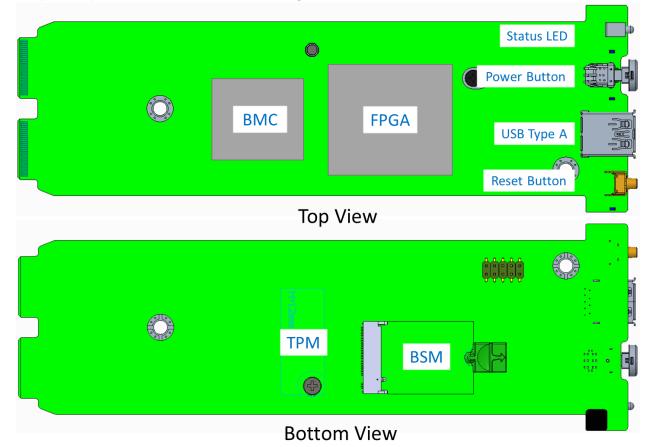

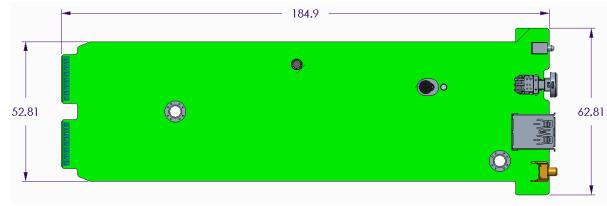

Figure 5.4: User Interface Card (UIC)

The UIC is a front accessible PCBA which plugs into the FDPB using SFF-TA-1002 card edge connector. Since the BMC sub-system is fully contained in the UIC, Grand Canyon now has the provision to upgrade the BMC solution without affecting the rest of the chassis design.

The dual and the single storage server configurations will deploy the full blown UIC.

There needs to be a second version called 'UIC w/o BMC' without the BMC, BSM, TPM circuitry. This version brings out the front panel elements only for use on the single storage server and JBOD configurations.

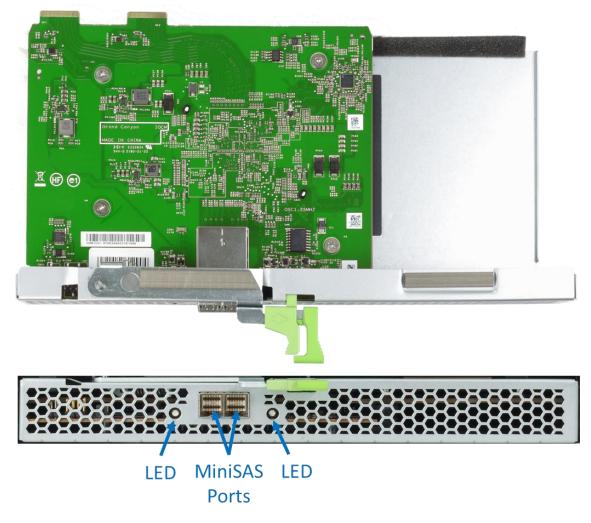

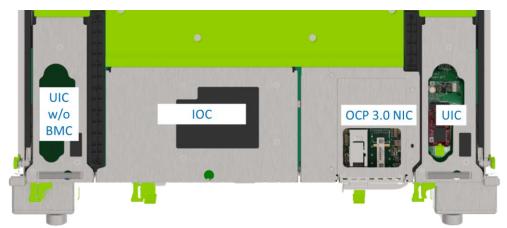

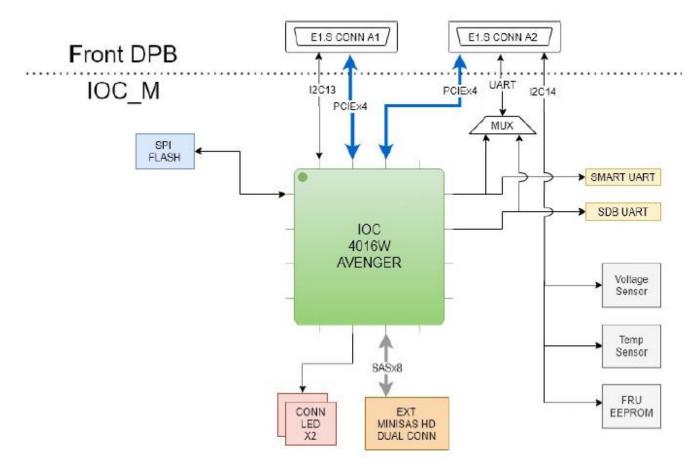

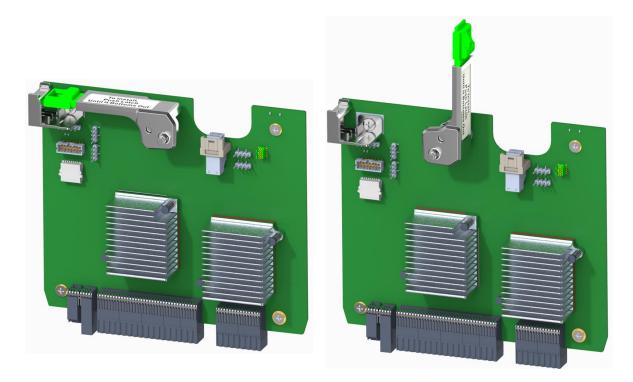

#### 5.2.4 IOC Module

The single storage server configuration used in Type 7 rack utilizes the IOC module to allow for SAS expansion from the single storage server to 2x JBOD chassis. The IOC module is a front accessible PCBA that plugs into the front drive plane board (FDPB) in-place of the 4x E1.S SSDs.

Figure 5.5: IOC Module

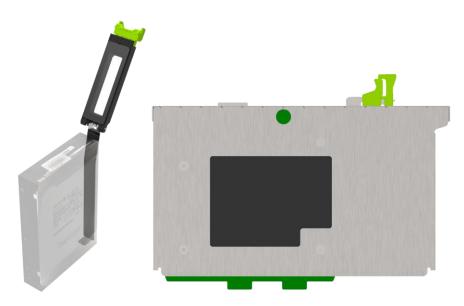

#### 5.2.5 E1.S SSD

As explained in the System Improvements section above, Grand Canyon will be designed with 4x E1.S SSDs per chassis, 2x per Barton Springs. E1.S has separate thermal case options. To make the thermal margins acceptable and to ensure we have a low fan RPM to ensure less vibration impact on the HDDs, it is imperative that we choose an option that's better than the bare PCB E1.S option.

To stay within the 4OU chassis form factor, the only front pluggable form-factors that work in Grand Canyon are the heatspreader option and the 9.5mm symmetric case. The heat-spreader option requires Meta to design its own bracket to mount the SSD and make it a front-loadable FRU. In lieu of this, Grand Canyon will opt to design in the 9.5mm E1.S SSD case option.

Figure 5.6: E.1S SSD

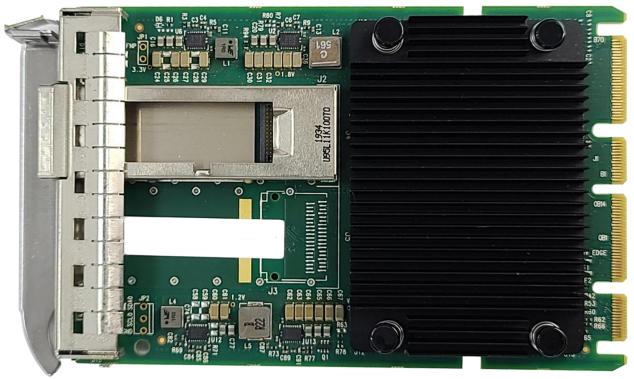

#### 5.2.6 OCP3.0 NIC

Grand Canyon hosts 2x single host OCP3.0 NICs in the small form factor (SFF), one NIC per Barton Springs.

Figure 5.7: OCP 3.0 NIC

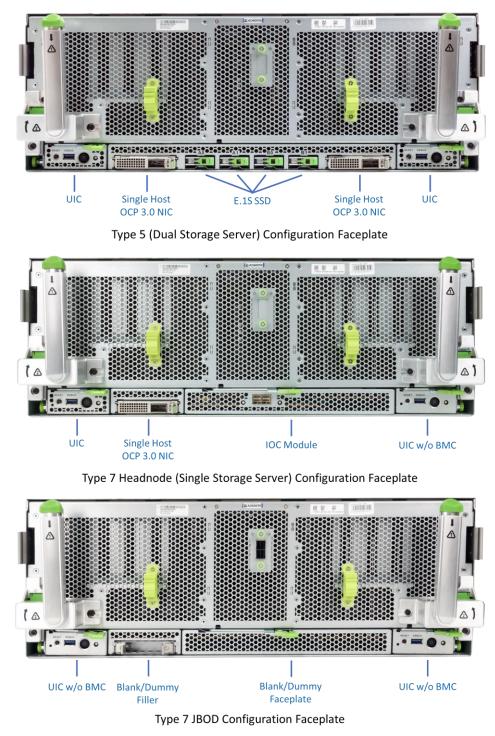

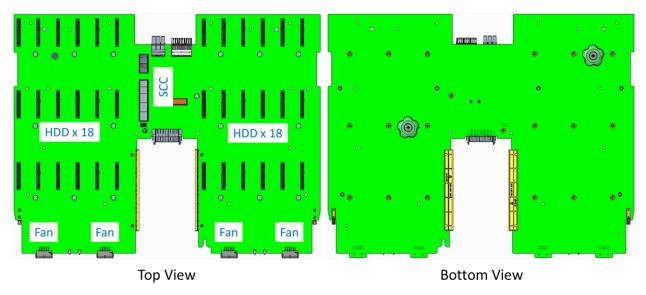

#### 5.2.7 Drive Plan Board (DPB)

The Drive Plane Boards (DPBs) sit at the base of the chassis. There are physically two Printed Circuit Boards (PCBs) that make up the drive plane board assembly, and they are connected via high speed connectors and an air baffle to create a single Field Replaceable Unit (FRU). The DPBs connect all of the boards in the system together, along with the drives, fans, etc. Its function is to support connectivity for the following:

- Single port SAS/SATA connections to HDDs (up to 72)

- PCIe Gen3 x4 connectivity to E1.S SSDs (up to 4) or PCIe Gen3 x8 connectivity to an IOC module (for JBOD expansion)

- PCIe Gen3 x16 to NICs (up to 2)

- Dual-rotor counter-rotating Fans (up to four)

- Drive power control (individual 5V/12V power control to each HDD and SSD slot)

- Sensors (ambient temperature, drawer open/intrusion)

• Incoming power (12V) distribution

Figure 5.8: Drive Plane Board (DPB) Assembly

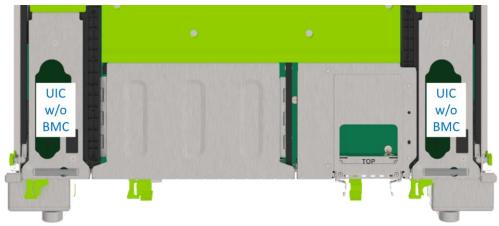

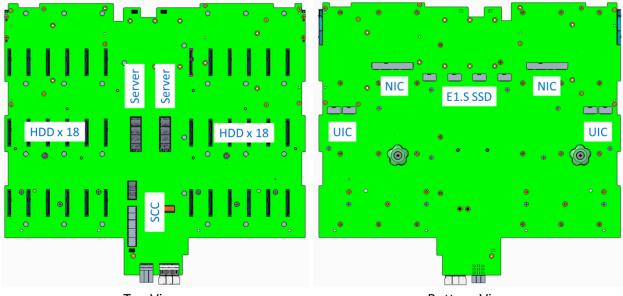

The population of these components is dependent on the overall system configuration (see Section). Shown below is a snapshot of the population options for the front accessible devices on the DPB. To enable this, there are 2 PCBA versions of the DPB assembly – one for Type 5 rack and one for Type 7 rack.

Type 5 (Dual Storage Server) Front Access Device Configuration

Type 7 Headnode (Single Storage Server) Front Access Device Configuration

Type 7 JBOD Front Access Device Configuration

Figure 5.9: DPB Front Access Device Configurations (Bottom View)

#### 5.2.8 Power Transfer Board (PTB)

The DPB shall be designed to distribute 12V as the main power plane to all loads in the system. In ORv2 rack, this DPB 12V can tie directly into the busbar 12V supply.

Grand Canyon PCBAs should be designed in such a way that it is flexible enough to be reused for the ORv3 design with 48V busbar. The Power Transfer Board serves the purpose of abstracting the busbar voltage change away from the rest of the system and delivering only a constant 12V to the rest of the system. It is recommended to physically fit in a 48V to 12V power conversion solution (either a Brick or Discrete) in a thermally optimal location behind the DPB so as to enable the same DPB and system PCBAs to be reused for an ORv3 configuration in the future. The expectation is to reuse the chassis, PCBAs and layout as-is without change, so Grand Canyon designed today should allocate room for the power conversion solution and enable a bypass option for use in the ORv2 case.

#### 5.2.9 Power Cable-Track and Power Delivery Board

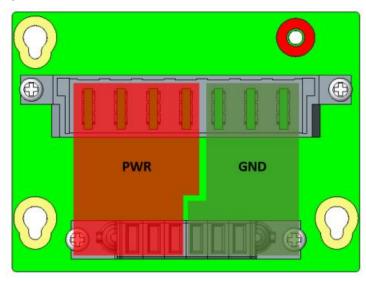

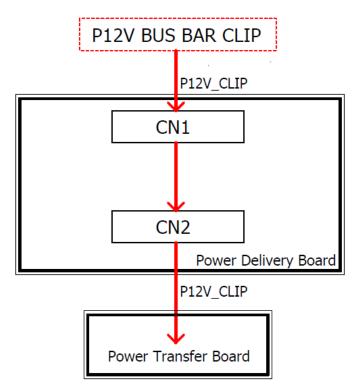

Figure 5.10: Power Delivery Board (PDB) & Power Transfer Board (PTB)

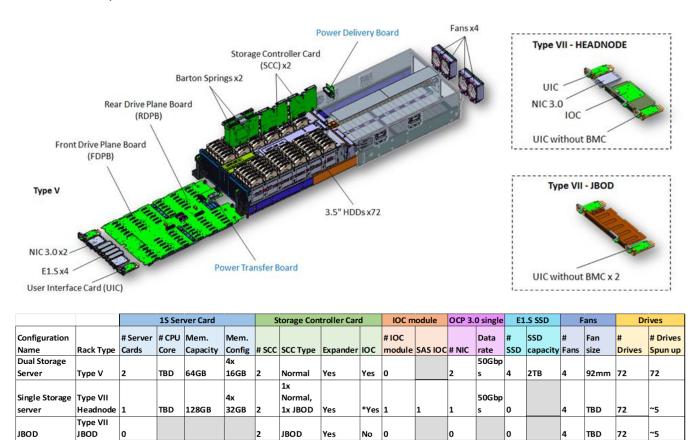

#### 5.3 System Configurations

This section outlines the different possible configurations of the overall system. There is a base Grand Canyon chassis configuration, but a few Field Replaceable Units (FRUs) can be installed to create simple JBODs, or single and dual integrated storage servers. Table 2 shows the current configurations considered for production.

Figure 5.11: Grand Canyon System Types and Configurations

The 3 configurations are differentiable from their faceplate as well as can be seen on the following pages.

Figure 5.12: Faceplate Configurations

#### 5.3.1 Dual Storage Server

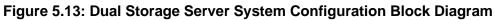

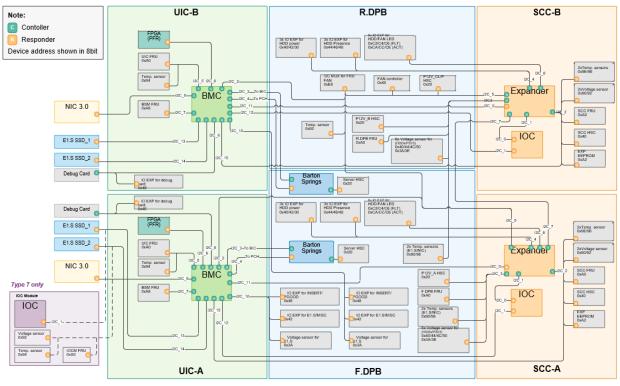

The nominal configuration described thus far is the Dual Storage Server configuration. This configuration is used for Type 5 racks. The block diagram for this configuration is shown in Figure 5.13.

#### 5.3.2 Single Storage Server

The Single Storage Server configuration is intended for applications that use a lower compute-tostorage ratio i.e., more disks per compute card. The block diagram is shown in Figure 5.14. This configuration serves as the head node for a Type 7 configuration, with several JBODs connected downstream to increase the number of drives behind a single server node. To connect all 72 drive slots within the chassis, the internal MiniSAS HD connector on both SCCs can be connected via an x4 cable.

Figure 5.14: Single Storage Server System Configuration Block Diagram

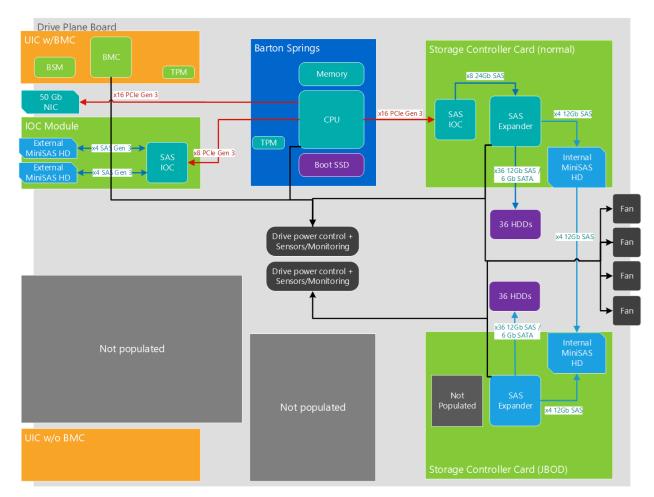

#### 5.3.3 JBOD

The JBOD configuration allows for an external compute module to connect to the Grand Canyon system. This compute module is cabled to the system via a SAS connector that is exposed on the front panel of the chassis.

In this configuration, the SCC does not have a SAS IOC populated. The server cards, NICs, SSDs are also not installed, and the fan control is coordinated by the SAS expander in lieu of the UIC w/o BMC.

Figure 5.15: JBOD Server System Configuration Block Diagram

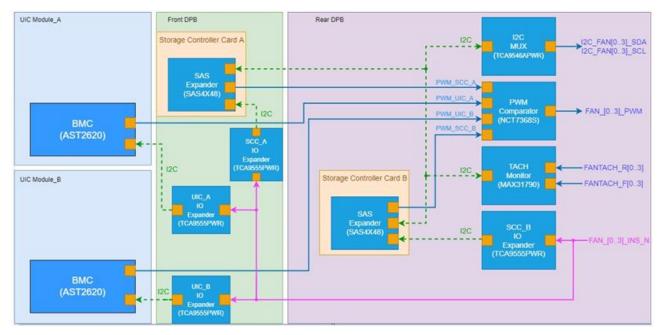

## 5.4 Systems Management Overview

The system is managed by two to four controllers (two BMCs and two expanders). Each of these controllers (referred to as peers) have ownership of part of the chassis. Interactions among these peers are limited to:

- 1. Insertion detection of all peers and Barton Springs

- 2. Heartbeat of all peers

- 3. Access to master hot swap controller (through multimaster I2C)

- 4. Access to TACH sensor (through multimaster I2C)

- 5. Fan speed control through PWM comparators

At a high level, the BMCs own the sensors on the UIC, Barton Springs, E1.S and the IOC chip on the SCC. The expanders own other sensors in the chassis, including HDD S.M.A.R.T. temperature.

The BMCs and SCCs all generate Pulse Width Modulation (PWM) for fan speed control using sensor inputs to determine fan speed. These PWM signals are compared using a PWM comparator and the highest requested fan speed is selected and used to control the setting for all 4 fan's PWM speed.

Each peer in the system monitors the insertion and heartbeat of other peers. If an expected peer is not presented or does not generate proper PWM, the firmware should increase fan PWM to a predefined value (e.g., 100%).

I2C device ownership information (per-configuration) can be found in the following Tables.

| BMC I2C<br>Bus # | I2C Devices (Slave Address)           | Comments                                                                     |

|------------------|---------------------------------------|------------------------------------------------------------------------------|

| 2                | BIC (0x40)                            | IPMB connection between BMC and BIC (Bridge IC) on Barton Spring Server Card |

| 3                | BS FPGA (0x1E)                        | Barton Springs FPGA Slave Address                                            |

|                  | Barton Springs FPGA Version<br>(0x80) | Barton Springs FPGA Version Register                                         |

| 4                | TMP75 (0x94)                          | UIC Temperature Sensor                                                       |

|                  | M24C64 (0xA0)                         | UIC FRU EEPROM                                                               |

| 5                | UIC FPGA (0x1E)                       | UIC FPGA Slave Address                                                       |

|                  | UIC FPGA Version (0x80)               | UIC FPGA Version Register                                                    |

| 6                | EEPROM (0xA8)                         | BSM FRU                                                                      |

| 7                | PCA9555 (0x4E)                        | I/O Expander for Decoding for Debug Card                                     |

BMC owned I2C devices:

| 8           | PLDM Sensor (0x3E)        | NIC Temperature and PLDM sensors               |  |

|-------------|---------------------------|------------------------------------------------|--|

|             | NIC FRU (0xA0)            | NIC FRU EEPROM                                 |  |

| 9           | ADC128 (0x3A)             | E1.S/IOCM and NIC Voltage Sensor (Main Source) |  |

|             | LTC2991 (0x90)            | E1.S/IOCM and NIC Voltage Sensor (2nd Source)  |  |

|             | TCA9555 (0x42)            | I2C to GPIO E1.S & MISC                        |  |

|             | TCA9555 (0x48)            | I2C to GPIO Insert & PWRGD                     |  |

| 10          | SCC Expander (0xE2)       | SCC Expander Slave Address                     |  |

| 11          | SCC IOC (0x68)            | SCC IOC Slave Address                          |  |

| 12 (Type 5) | NVMe SMBUS Address (0xD4) | E1.S 0 Temperature Sensor                      |  |

| 12 (Type 7) | IOCM IOC (0x68)           | IOCM IOC Slave Address                         |  |

| 13 (Type 5) | NVMe SMBUS Address (0xD4) | E1.S 1 Temperature Sensor                      |  |

| 13 (Type 7) | ADS1015 (0x92)            | IOCM Voltage Sensor (Main Source)              |  |

|             | LTC2990 (0x98)            | IOCM Voltage Sensor (2nd Source)               |  |

|             | TMP75 (0x94)              | IOCM Temperature Sensor                        |  |

| M24C64 (0xA0) | IOCM FRU EEPROM |  |

|---------------|-----------------|--|

|               |                 |  |

# 6. RACK COMPATIBILITY

**NOTE**: To achieve interoperability, new specifications and products seeking recognition shall be compatible with an OCP adopted architecture: ORv2, ORv3, or OpenEDGE architectures. This is required for storage enclosures and systems, rack frames, and any enclosure which holds a server sled or edge device sled. Compatibility is also desired of server sleds and edge sleds. All other device types not listed are not required to support this.

The Grand Canyon platform will be used in a few configurations to meet the needs of several rack types, as outlined in future sections. Grand Canyon is ORv2 compliant.

# 7. RACK IMPLEMENTATION

The Grand Canyon platform will be used in a few configurations to meet the needs of several rack types, as outlined in the following sections.

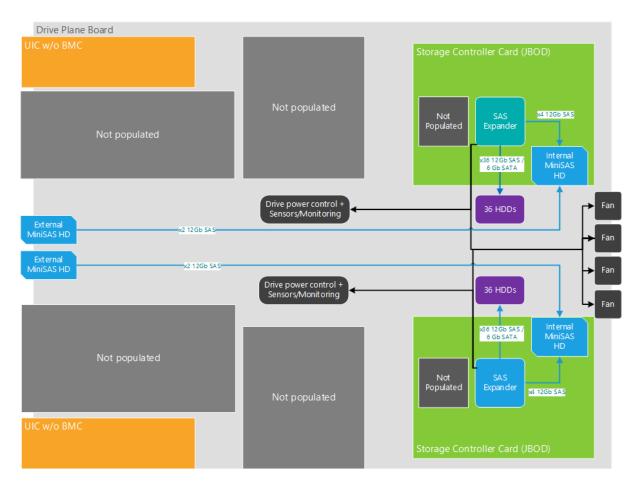

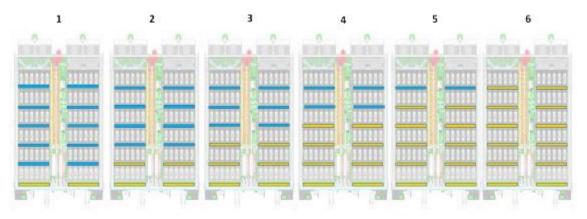

# 7.1 Type 5

In this configuration, there are two storage servers with 36 drives each inside the Grand Canyon chassis. The compute portion is an integrated 1S server.

Figure 7.1: Type 5 Rack Configuration

# 7.2 Type 7

There will be two different Grand Canyon configurations populated within a rack of this type. There will be a main Grand Canyon unit with 1 compute card, and two Grand Canyon JBODs (without a compute card) connected behind this, for a total of 216 drives in each functional system. In the base unit, there will be a single 1S server that connects to all drives in the base chassis.

Figure 7.2: Type 7 Rack Configuration

# 7.3 Compatibility with Open Rack Standard

All specifications and products seeking product recognition for use in Open Rack shall comply with Open Rack specification revision 2.0.

# 8. SYSTEM INTERACTION AND SERVICEABILITY

## 8.1 Labeling of Logical Domains

The drive domains are physically divided between the front and rear of the chassis via the two DPBs. The compute modules are separated in a left/right fashion. On the following page, Figure 8.1 shows the 2 logically separate systems using yellow and blue highlights. Consequently, the correct logical division of the two domains must be made clear through highly visible labeling.

Type 7

Figure 8.1: System Drive Domains

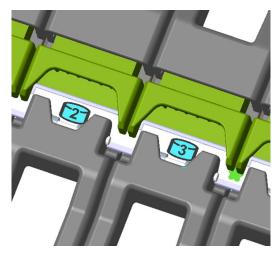

One important design point that makes drive swaps intuitive is to implement light pipes near the drives to bring the light from the activity/fault LEDs to a visible location. If the labels are metal-backed or are otherwise normally opaque, but clear over the light pipe area, this will help contain the light. Also, the drive numbers can also be opaque, essentially creating a backlit number for the drive slots.

The shape pointing to the drive should be a trapezoid instead of a triangle to maximize space for drive numbers for clear identification of the drive slot, while at the same time making the direction of the indicator obvious. A close-up of the drives showing these indicators is shown in Figure 8.2.

Figure 8.2: Drive Number Indicators

# 8.2 LEDs and Buttons

This section gives an overview of the various LEDs and buttons within the Grand Canyon system.

8.2.1 Front Panel Buttons and LEDs

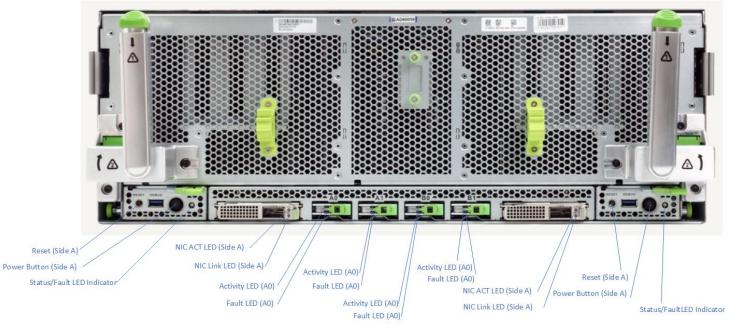

In all chassis configurations, there will be a power button with integrated system power LED, reset button, a bicolor system status/fault LED, and a USB debug port per host/bmc/expander. There will be two instantiations of the front panel, one for each of the two logical systems in the physical chassis. These features will all be located on a User Interface Card (UIC).

There are two NIC slots per logical system. As seen in Figure 8.3 below each NIC, if populated, has an activity LED and a Link LED. There are four E1.S drives per system, 2 per logical domain. Each SSD has an activity LED and a fault LED.

Figure 8.3: LED Designations

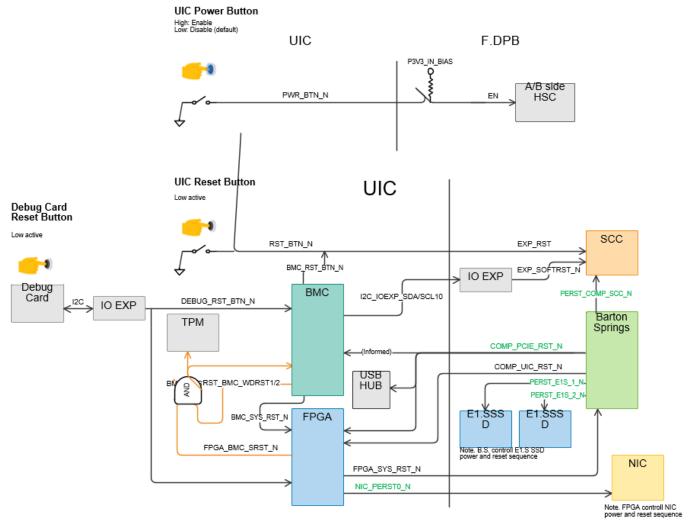

# 8.2.1.1 Power Button

The functionality of the power button is to physically turn on/off the hot swap controller that gates the power to one server subsystem of the Grand Canyon system. This is used for service events, (such as server replacement or SCC replacement) to allow the technician to power off the server subsystem to perform this action. The button shall be a push-on/push-off type switch, so that the state is persistent until an operator pushes the button again. The system should ship with this button in the "ON" position.

### 8.2.1.2 Power LED

In order to minimize the space needed and to make servicing the system intuitive, the system power LED should be integrated into the power button. The LED shall be blue. The LED will have the ability to be controlled by both the SCC and the BMC to allow blink patterns for system identification. A blink pattern of 1s on, 1s off will indicate unit identification.

### 8.2.1.3 Reset Button

The reset button shall be a momentary on push button switch with a black plunger. This reset button is routed to the SCC card to serve as a hard reset signal for the expander. The reset button on the USB debug card can be used along with UART select function key to reset the BMC or the server card.

The system status/fault LED informs the user of the system health and whether there is a problem with the system. This will be driven by the expander or the BMC to indicate any faults that happen with the

sensors monitored by them. The LED shall be solid yellow during a fault and solid blue indicating everything's good.

| вмс     | Barton<br>Springs | Event                                                       | Bicolor LED        |

|---------|-------------------|-------------------------------------------------------------|--------------------|

| off     | off               | system off                                                  | Off                |

| Booting | off               | BMC booting                                                 | Solid Yellow       |

| on      | off               | BMC ready, Barton Springs power off                         | Blinking<br>Yellow |

| on      | on                | Barton Springs ready, no faults                             | Solid blue         |

| on      | on                | BMC Fault critical (BMC health, sensors health, NIC health) | Solid Yellow       |

| on      | on                | Barton Springs Health/Fault Status Critical                 | Solid Yellow       |

| on      | off               | BMC Fault critical (BMC health, sensors health, NIC health) | Solid Yellow       |

| on      | on                | Expander Fault critical (Expander, sensors health)          | Solid Yellow       |

| on      | on                | System identification                                       | NA                 |

### 8.2.1.5 USB Debug Port

Grand Canyon Platform has one OCP debug USB connector per compute card/BMC/Expander located at the front panel. The connector supports the OCP USB3.0 debug card. Information in regards to the host and their POSTcodes/SEL/config are displayed thru the LCD of the OCP USB3 debug card. The UART select button on the card allows the users to walk through the UART console of the host, BMC or the Expander for their information.

The power and reset push buttons on the USB debug port should apply to the host, BMC or the expander based on the UART selector option. The USB port on the debug card is purely meant for BMC. Users may insert a thumb drive here to allow data transfer to/from USB etc.

### 8.2.1.6 SSD LEDs

The E1.S SSD has two LEDs – Power and Fault/Locate. The Power LED is a mono-colored blue LED which indicates if the system is currently powered. The Fault/Locate LED is a mono-colored amber LED which indicates SSD fault locations along with drive identification.

| System Status | Drive Status    | Power LED | Fault/Locate LED |

|---------------|-----------------|-----------|------------------|

| Off           | Service Allowed | Off       | Off              |

| On            | Drive Okay      | On        | Off              |

| Off           | Fault           | Off       | On               |

| On            | Locate          | On        | Blink            |

| Off           | Locate          | Off       | Blink            |

| On            | Fault           | On        | On               |

### 8.2.1.7 NIC LEDs

The NIC LEDs will follow the OCP NIC 3.0 specification and will have two LEDs – Link and Activity. The Link LED is a bi-colored green/amber LED which denotes link status. The Activity LED is a mono-colored green LED which shows whether the link is in use.

| Link Status            | Link Activity | Link LED | Activity LED          |

|------------------------|---------------|----------|-----------------------|

| No Link                | No            | Off      | Off                   |

| Link at Max Speed      | No            | Green    | Off                   |

| Link at Max Speed      | Yes           | Green    | Blink<br>(½Hz - 5 Hz) |

| Linked below Max Speed | No            | Amber    | Off                   |

| Linked below Max Speed | Yes           | Amber    | Blink<br>(½Hz - 5 Hz) |

#### 8.2.1.8 IOC Module LEDs

There are 2 mini-SAS HD connectors on the IOC modules to connect the T7 head node to 2x JBODs.

There is a single blue/yellow LED per MiniSAS HD port. The behavior of the LED is described below on the following page.

- Solid blue All four lanes up and linked at 12Gb SAS

- Solid yellow Fault/warning

- Off No cable present/link is down

#### 8.2.3 HDD LED behaviors

Each drive slot has a single light pipe with an LED indication as to the state of the drives. The behaviors are described below, and summarized in a table to identify the various states:

- Drive powered off/ not installed No LED illuminated

- Drive powered on and PHY linked to Storage Controller Card Blue LED illuminated

- **Drive fault** Yellow LED illuminated

- **Drive identify** Blinking yellow LED. If a drive is powered on, this behavior will show the yellow LED illuminated for one second, blue LED illuminated for one second, repeating. If the drive is powered off, this would appear as a yellow LED on for one second, off for one second, repeating.

The following table identifies different conditions within the box, and the respective behaviors of the LEDs.

| Status                                         | LED<br>Indication | Blue (ACT)               | Yellow (Fault)           | Mechanical           | Expander<br>code |

|------------------------------------------------|-------------------|--------------------------|--------------------------|----------------------|------------------|

| No Drive                                       | No                | Off                      | Off                      | Empty Slot           | No               |

| Drive Not Seated (or<br>backwards)             | No                | Off                      | Off                      | Latch Won't<br>Close | No               |

| Drive Powered On, no Link                      | Yes               | Blink<br>(1s on, 1s off) | Off                      |                      | Yes              |

| Drive Powered On,<br>SAS/SATA Link established | Yes               | On                       | Off                      |                      | Yes              |

| Drive Faulted                                  | Yes               | Off                      | On                       |                      | Yes              |

| Drive Identify<br>(Drive Off / Not Present)    | Yes               | Off                      | Blink<br>(1s on, 1s off) |                      | Yes              |

| Drive Identify (Drive On)                      | Yes               | Blink<br>(1s on, 1s off) | Blink<br>(1s on, 1s off) |                      | Yes              |

### 8.2.4 Fan Module LEDs

The fan modules have LED indications to indicate the health of the fans:

- Blue When illuminated, indicates fan module health is good (actively controlled via the SCC)

- Yellow When illuminated, indicates a fan fault

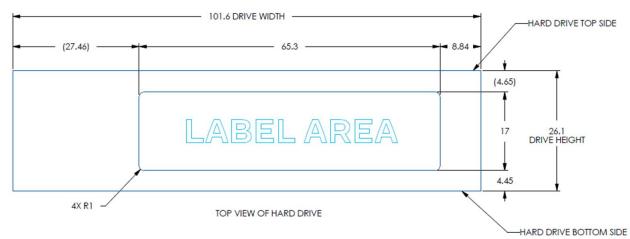

# 8.3 Hard Drive Serial Number Window

Grand Canyon features drive latches that have openings to allow the operator to scan the drive serial number if it confirms to the open window. The details of this window are shown in Figure 8.4.

Figure 8.4: Hard Drive Serial Number Window

# 8.4 Service Operations

The Grand Canyon system provides hot swap controllers on the power rails, but the system will not support hot swap of the SCC, NIC or compute module due to PCIe surprise removal/insertion events. This functionality can be added later if needed, as the electrical subsystem supports this. The drive slots, however, all support hot plug.

### 8.4.1 HDD Replacement

The drives are all hot pluggable, and it is up to the service flow if the drives are spun down or not before removal. To replace a drive, the latch should be opened and pulled up to remove the drive from the system. By pulling up on the latch once it is opened to a vertical position, the drive is partially removed from the system to allow easy access to grab the drive. A new drive can then be inserted, and then the latch can be closed to lock the drive into place.

Figure 8.5: HDD Replacement

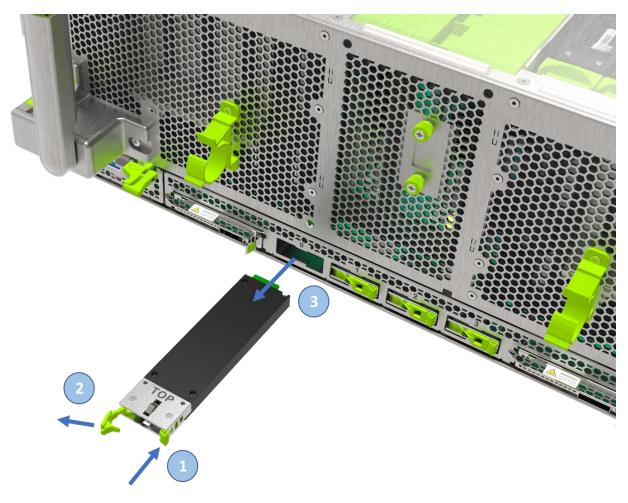

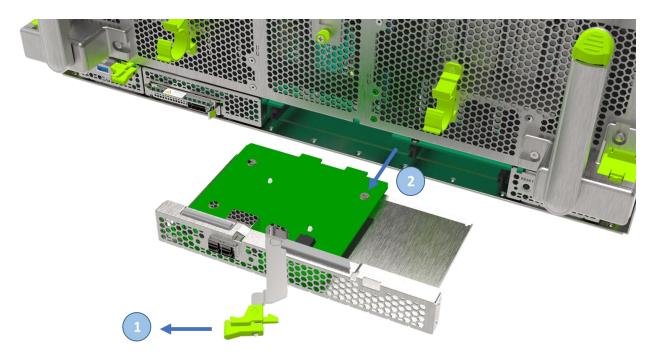

8.4.2 SSD Replacement

SSDs are hot-swappable so there is no need to power off the system before an SSD swap. To replace the E1.S SSD, release the ejector latch and pull the SSD out from the front panel. Replace a new SSD in its place and lock in the ejector latch.

Figure 8.6: SSD Replacement

8.4.3 SCC Replacement

To replace the SCC, the A/B domain should be shut down via the power button on the front panel module. The power button is illuminated blue while the power is on, and turns off when the power is off to that portion of the system. The SCC can then be removed, a new module installed, and then the power button can be pressed to turn the system back on.

To remove the SCC, first remove the air baffle above it. Pull the latch tab on the module and rotate the ejector until it is fully disengaged. Pull on the ejector handle to remove the SCC. To install, guide the SCC into the slot and rotate the ejector until it fully bottoms out. Place the air baffle back on.

Figure 8.7: SCC Replacement

8.4.4 UIC Replacement

To replace the UIC, the A/B domain should be shut down via the power button on the module. The power button is illuminated blue while the power is on, and turns off when the power is off for that portion of the system. The UIC can then be removed, and a new UIC module can be installed. The power button is pressed to turn the system back on. To replace the UIC, release the ejector latch and pull the UIC out from the front panel. Replace a new UIC in its place and lock in the ejector latch.

Figure 8.8: UIC Replacement

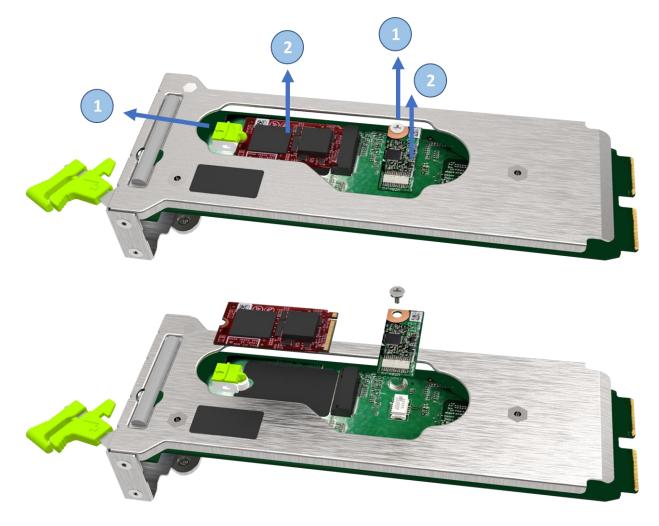

# 8.4.5 UIC TPM & BSM Replacement

The UIC has a removable TPM (Trusted Platform Module) and BSM (BMC Storage Module).

To replace the TPM, unfasten the screw holding it down and pull it away from the UIC. Replace it with a new TPM by aligning it with the connector and pushing it down. Secure with the screw.

To replace the BSM, pull back on the spring loaded latch to release the module. Pull the BSM out of the connector and away from the UIC. To replace the BSM, install it into the connector and push down on it near the spring loaded latch until it clicks into place.

Figure 8.9: UIC TPM & BSM Replacement

8.4.6 NIC Replacement

To replace the NIC, release the ejector latch and pull it to unseat the NIC from the connector and remove it out. Replace with a new NIC and follow the same steps in reverse order to latch the NIC onto the system. It is recommended for the NIC to be swapped only when the system is powered off.

Figure 8.10: NIC Replacement

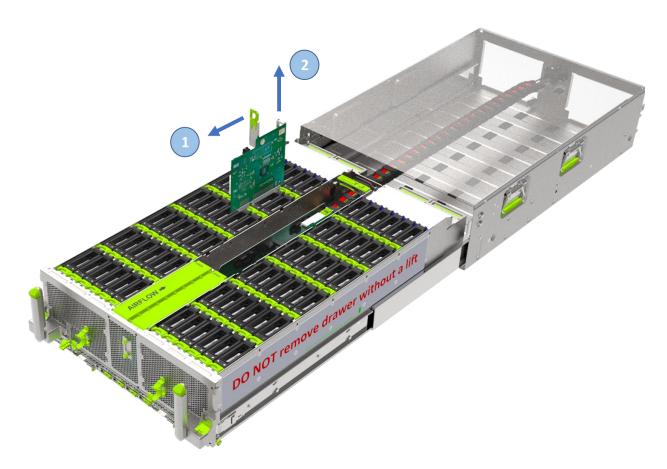

8.4.7 Barton Springs Replacement

To replace the compute module, the A/B domain should be shut down via the power button on the front panel module. The power button is illuminated blue while the power is on, and turns off when the power is off to that portion of the system. The compute module can then be removed, a new module installed, and then the power button can be pressed to turn the system back on.

The SSD and DIMMS are FRUs, and can be replaced separately if they are identified as failed instead of the compute module itself. To remove the compute module, first remove the air baffle above it. Then, pull the latch tabs on both ejectors and rotate the ejectors until they are fully disengaged. Pull on the ejector handles to remove the compute module. To install, guide the module into the slot and rotate ejectors until they fully bottom out. Place the air baffle back on.

Figure 8.11: Barton Springs Replacement

8.4.8 IOC Module Replacement

On the T7 head node configuration, the IOC module can be replaced on the front panel after the system A/B power is turned off. The power button is illuminated blue while the power is on, and turns off when the power is off. Once the power is off, the IOC module can be ejected with the help of the ejector latch. Once a new card is loaded in, power can be turned back on for the system.

Figure 8.12: IOC Module Replacement

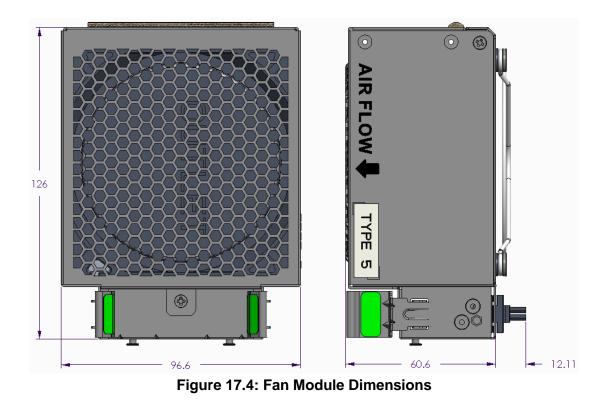

8.4.9 Fan Module Replacement

The fan modules are hot-swappable from the rear of the chassis. Each fan module consists of one fan integrated into an easy to service module. Each fan is a dual rotor setup and the fan module as is will be a FRU. In the Type 7 configuration there may only be a single rotor fan contained in the module.

If the fan is removed for too long, the remaining fan module may increase its fan speeds in an effort to keep the system within its thermal operating limits. In order to remove the fan, squeeze the two latches on the bottom of the module inward. Pull on the module until it comes out. To install a new fan, just slide it into the chassis until the latches click into place.

Figure 8.13: Fan Module Replacement

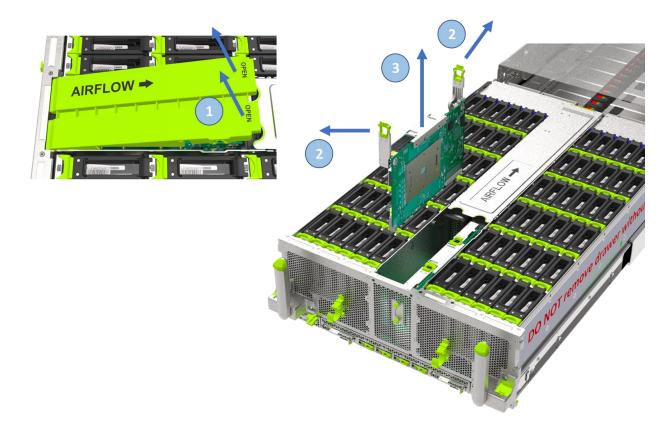

# 8.4.10 Fan Louver & Honeycomb Replacement

Behind the fans are a set of louvers and honeycomb. The purpose of the honeycomb is to reduce acoustic vibration from the fans. The purpose of the louvers is to reduce backflow in the case of fan failure or in a service scenario.

First, remove the fan module from the chassis. In order to service the louver module, press on the two tabs on top of the module and pull it out. Once the louver module is out, you can remove the honeycomb. To remove the honeycomb, pull on the tab at the top of the honeycomb module and pull it out. In order to replace both modules, repeat the steps in reverse.

Figure 8.14: Fan Louver Module Removal

Figure 8.15: Fan Honeycomb Module Removal

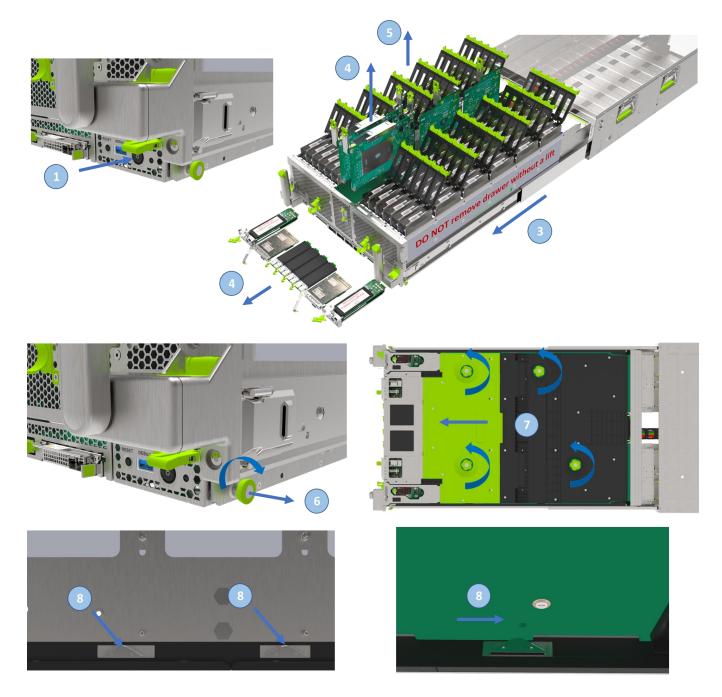

### 8.4.11 Drive Plan Board Replacement

There are two DPBs in the system, but these are always replaced as a single unit. For all intents and purposes, these should be considered as a single FRU – it is only divided due to manufacturing limitations. Replacing the DPB should be a rare event, but if it's required, perform the following:

- 1. Power down both sides of the system via the power buttons on the front panel.

- 2. Unplug the cables on the front of the system.

- 3. Pull the drawer out to its fully extended position.

- 4. Remove the SCCs, NICs, SSDs, UICs and compute modules.

- 5. Unlatch and lift up on all of the drives, which will hold them up and away from the DPB.

- 6. Pull out and rotate the retaining plunger on each side of the chassis until it is locked in the open position.

- 7. Unscrew four thumb screws on the bottom of the DPB assembly, and slide the DPB towards the front of the chassis to remove the board.

- 8. Install the new DPB assembly by aligning along the DPB card guide and sliding back in until the DPB engages with the power delivery board.

- 9. Follow steps 1-6 in the reverse order to put all of the components back into the system.

Figure 8.16: Drive Plane Board Replacement

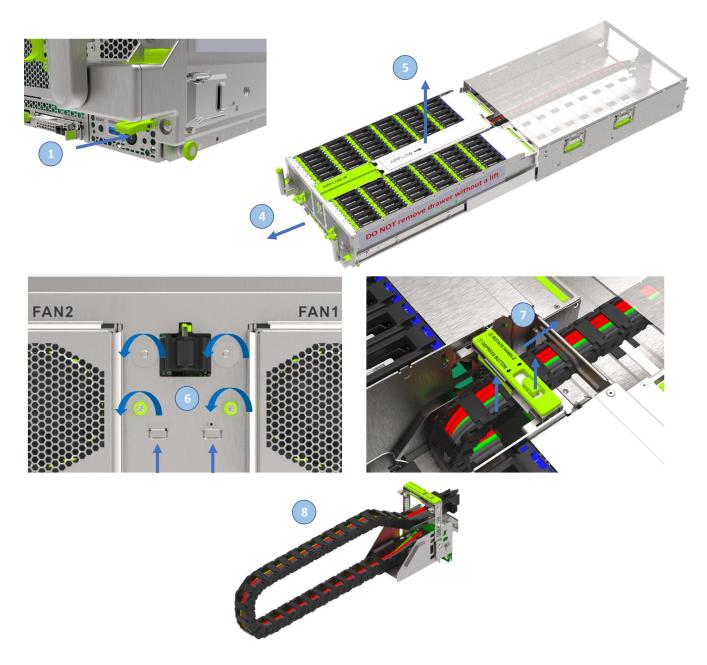

8.4.12 Cable Track and Power Delivery Board Replacement

There is one bus bar power module consisting of medusa cable track and power delivery board. Perform the following to replace the bus bar power module.

- 1. Power down both sides of the system via the power buttons on the front panel.

- 2. Unplug the cables on the front of the system.

- 3. Remove the entire chassis from the rack.

- 4. Pull the drawer out to its fully extended position.

- 5. Remove the rear airflow baffle by lifting it at the finger touchpoints.

- 6. Disconnect the bus bar bracket and connector from the chassis. First, remove the two screws attaching the connector to the chassis. Then, release the two captive screws holding the bracket and lift it up, ensuring the two tabs on the bottom are disengaged.

- 7. Release the mechanism to remove the bus bar power module. Lift up the locking tab on the power module, press on the button under the handle, and push the handle forward.

- 8. Pull the bus bar power module out of the drawer.

- 9. Follow step 1-6 in the reverse order to put all of the components back into the system.

Figure 8.17: Cable Track and Power Delivery Board Replacement

# 9. SYSTEM PERFORMANCE

Performance degradation at a system level can be due to interface bottlenecks like PCIe. SAS interfaces, or due to component bottlenecks like IOC IOPS limit or CPU performance or drive performance degradation due to vibrations. The system must be designed so that there is minimal degradation due to the system design from any of these aspects.

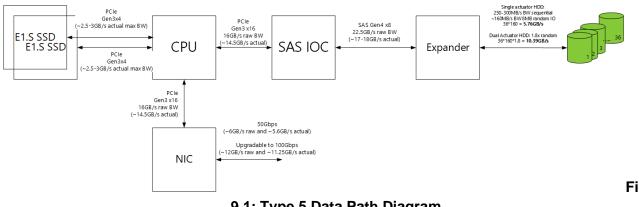

# 9.1 Designing the system interfaces without bottlenecks

Grand Canyon is a HDD storage server/JBOD and the data stored on HDDs are the IO movers on the system. Considering the typical and worst case workloads, the critical components were selected to ensure the Grand Canyon system has no interface bottlenecks for any of the configurations discussed so far.

Grand Canyon Type 5 configuration will be designed to accommodate Dual-actuator or Split-actuator HDDs and will provide optionality to allow for NIC upgrade to remove system interface bottlenecks.

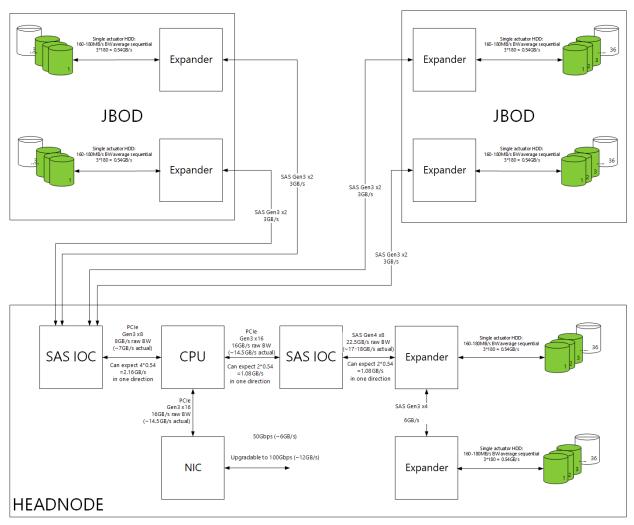

9.1: Type 5 Data Path Diagram

Figure

The Grand Canyon Type 7 configuration conserves power by actively powering off HDDs. At any given point in time, there will be only 4 HDDs per Expander powered on in the Type 7 configuration. Out of the 4 HDDs, only 3 HDDs will be actively serving IO and the 4<sup>th</sup> HDD is reserved to take over when an already active HDD is deemed bad and needs replacement.

Figure 9.2: Type 7 Data Path Diagram

# 9.2 HDD performance degradation due to vibrations

Several areas contribute to negative drive performance impact, such as surrounding disk drives and the fans. The system must be designed so that over the operating conditions, all drives are able to perform within the specified limits as outlined below.

The only exception to the requirements described above are during drawer removal and insertion operations for service. During these events, it is acceptable for the drive performance to be affected, but there must be no damage to the drives themselves (for example, head touchdown, etc.).

9.2.1 Normal Operating Environment (sustained operating conditions)

The system should have performance degradation <5% average across the system (up to 35C, 1800m/6,000ft altitude), where every slot conforms to this <5% performance degradation requirement.

# 9.2.2 Unsustained Operating Conditions

The system should have performance degradation <10% max for any drive slot, and <10% average across the entire system. Examples of these operating conditions include single and multiple fan rotor failures, chassis intrusion/drawer pull-out during hot servicing of drives. This operating point includes the maximum temperature and altitude operating points (up to 35C, 1800m/6,000ft altitude). The maximum service time by design should accommodate 10 mins of drawer pullout with the system remaining operational and no components reaching critical thermal conditions.

# 9.2.3 Design Criteria to Enable Chassis Longevity

Grand Canyon will be designed to support dense HDDs (advent of energy assisted recording) and shall be designed to adopt the projected HDD capacities for a 5 year lifetime from its release date. To that point, adding support to the chassis for a drive capacity 3 or 4 or 5 years out in time is a waste today. Grand Canyon shall be designed with multiple options to dampen/attenuate structural and acoustic vibrations seen by the HDDs and enable phasing in these options with HDD capacity bump-up as needed, to ensure that the above performance degradation limits are met.

# **10. ELECTRICAL DESIGN**

This section details the electrical design of the major system boards, the systems management topology, and other system details.

# 10.1 PCIe Topology

### 10.1.1 PCIe Mapping

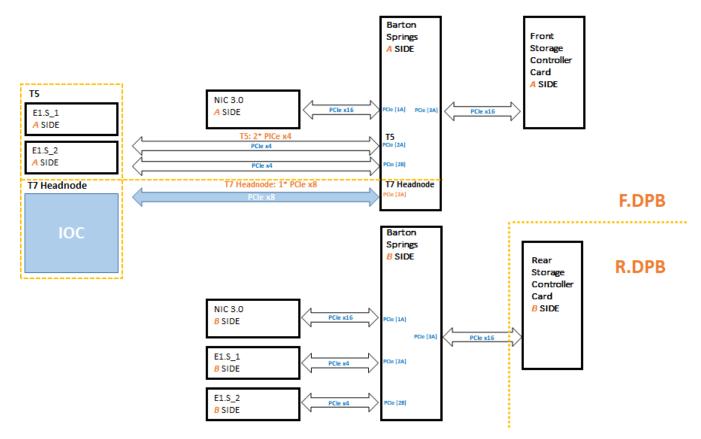

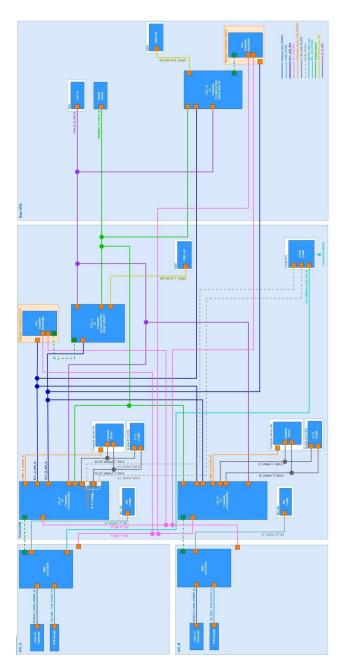

The PCIe topology of the Grand Canyon system is shown in the diagram on the following page.

Figure 10.1 System PCIe Topology

The PCIe key commodity mapping is shown on the next page.

|                  | A Side       |            | B Side     |          |

|------------------|--------------|------------|------------|----------|

|                  | M.2 SSD      | E1.s SSD_0 | E1.s SSD_1 | NIC card |

| location         | On BS Server | A1/B1      | A0/B0      | N/A      |

| root port        | 63:02.0      | 63:00.0    | 63:01.0    | 15:00.0  |

| end device       | 66:00.0      | 64:00.0    | 65:00.0    | 16:00.0  |

| Nvme list        | nvme2n1      | nvme1n1    | nvme0n1    | N/A      |

| Support hot plug | NO           | YES        | YES        | NO       |

Figure 10.2: Key Commodity Mapping - PCIe Devices

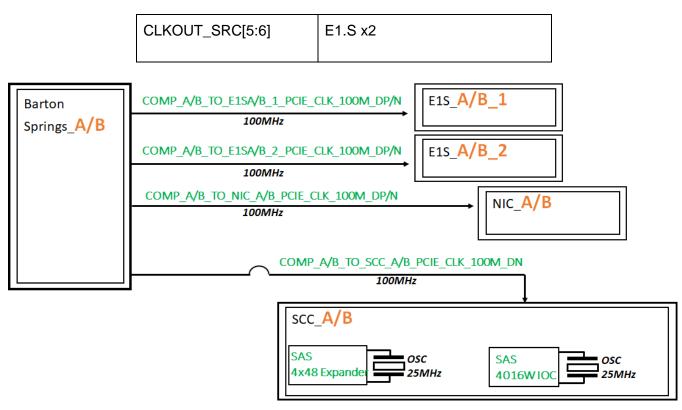

# 10.1.2 PCIe Clocks and Resets

The PCIe clocks and resets originate from the compute server, and connect to the various PCIe devices in the system. The routing of the clocks and resets is shown below in Table 10.1 and Figure 10.1. Due to the nature of PCIe reset signals, buffers with Schmitt Triggers should be used if the traces are deemed too long to have a sufficient edge rate.

### Table 10.1: PCIe Clock Info

| PCH clock output | Destination     |

|------------------|-----------------|

| CLKOUT_SRC_3     | SCC board (IOC) |

| CLKOUT_SRC_4     | OCP NIC 3.0     |

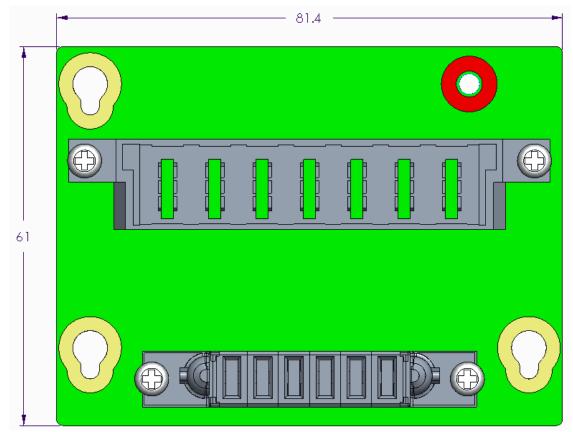

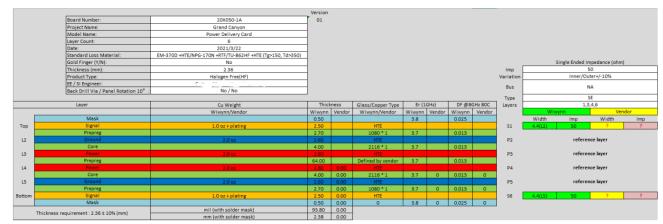

Figure 10.3: PCIe Clock Topology